# Pollex DFE/SI 를 활용한, SI/PI/EMC 대응 설계

- POLLIWOG Corporation.

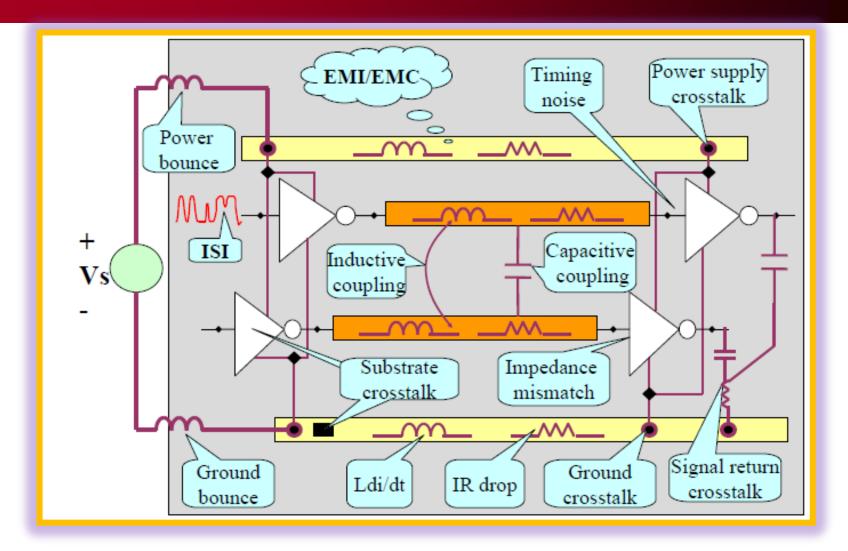

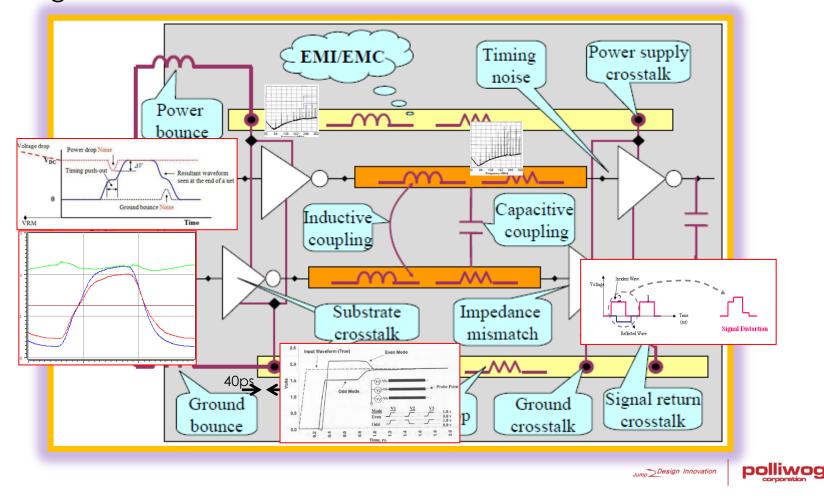

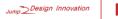

## SI/PI/EMI Issue in PCB

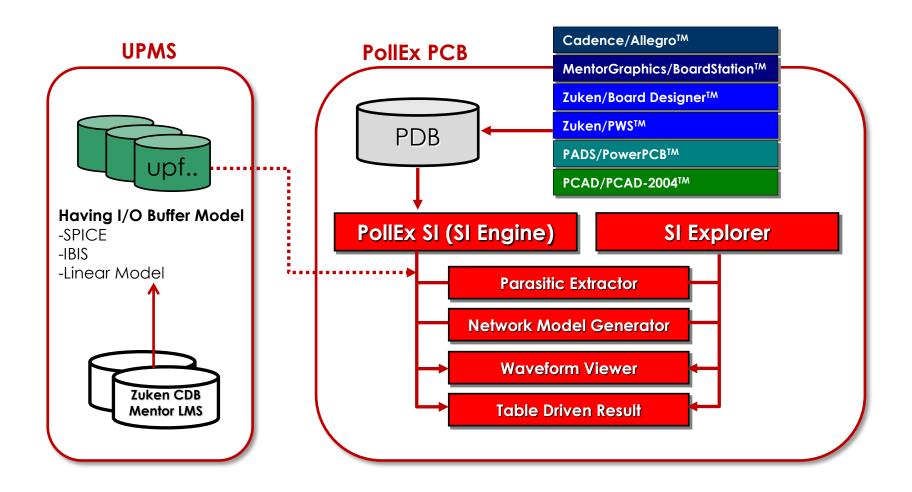

## **PollEx Signal Integrity**

- Transmission Line Analysis: Routed Net Impedance, Delay 분석, TLM Model 생성/관리

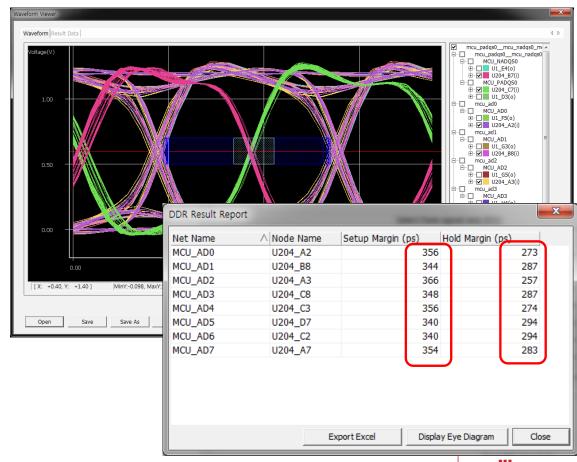

- Network Analysis: 신호 Eye Diagram, Setup/Hold Margin 및 Noise Analysis

- Data Line Analysis: DDR Data Line의 Byte별 Analysis 일괄 수행

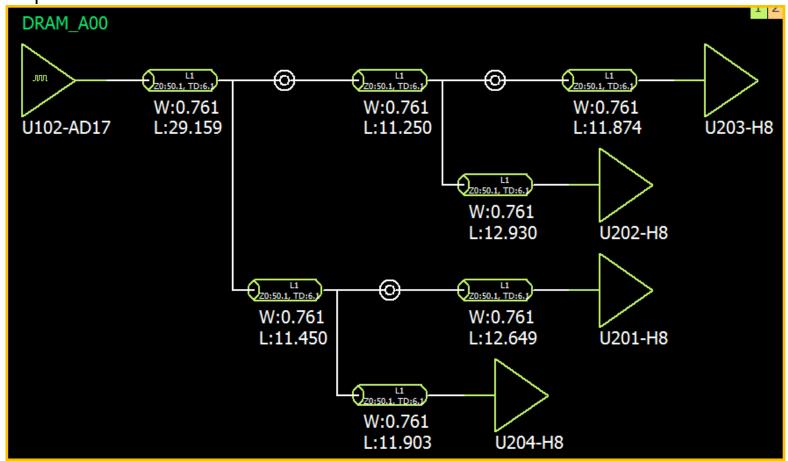

- ADD/CMD/CNTR Line Analysis: DDR ADD/CMD/CNTR Line의 Byte별 Analysis 일괄 수행

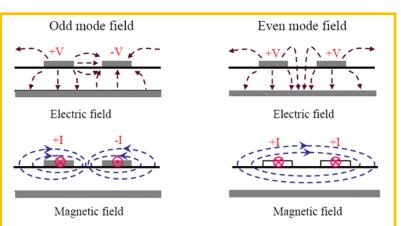

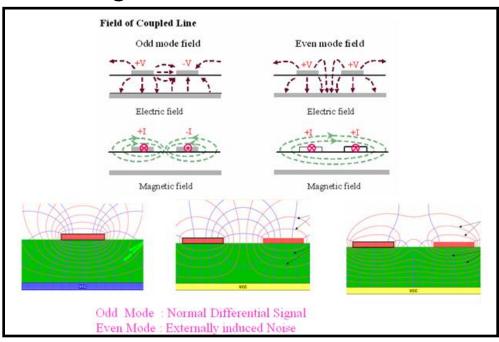

- Crosstalk Analysis: Routed Net Coupling 분석, Odd/Even Mode Crosstalk 분석

- , Net Topology Analysis: Net Topology 분석 및 수정/해석 기능

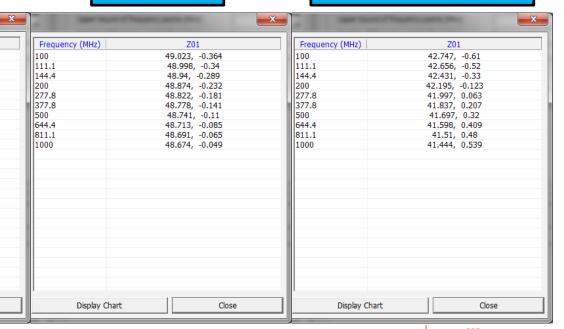

Frequency (MHz)

Display Chart

100

111.1

144.4

277.8

377.8

644.4

500

200

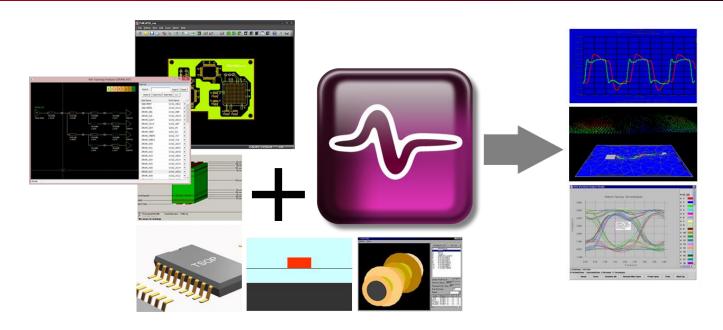

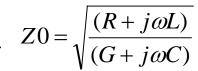

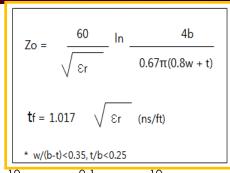

### Transmission Line Analysis

- Analysis PCB trace etching effect

- Analysis GND guard effect

Z0 = L/C **∝** W, h, t

1\_0.09

52.691, -1.789

52.597, -1.686

52.36, -1.467

52.11, -1.23

51.902, -1.019

51.735, -0.857

51.587, -0.728

51.482, -0.629

51.394, -0.548

51.326, -0.484

Close

Transmission Line Analysis-Display Results

© Model © Item

Resistance (Ohm/cm)

Inductance (nH/cm)

Capacitance (pF/cm)

Conductance (mS/cm)

DC Resistance (Ohm/cm)

C11

Skin Depth (m)

Delay (sec/m) TD1 Velocity (m/sec) V1 Attenuation (dB/m)

#### Transmission Line Analysis

- Impedance Mismatch

#### Transmission Line Analysis

- Impedance Match

#### Transmission Line Analysis

- Impedance Mismatch

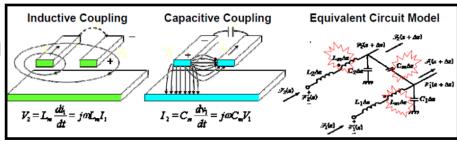

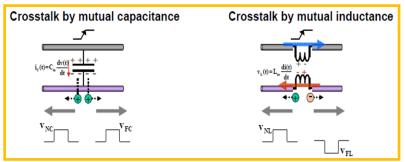

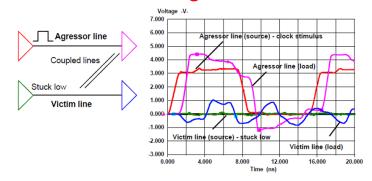

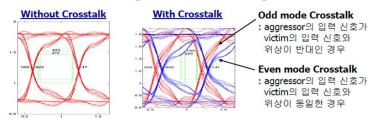

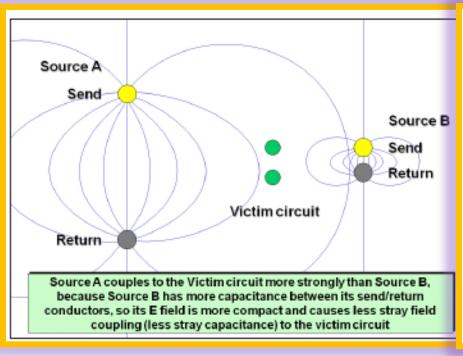

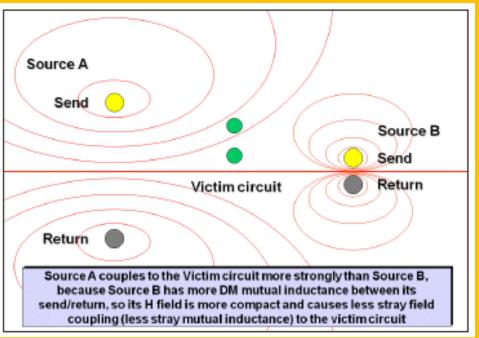

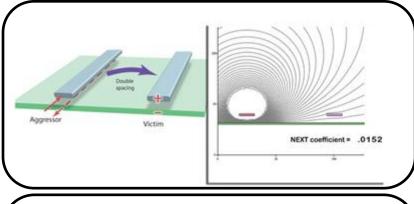

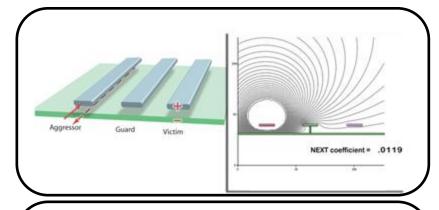

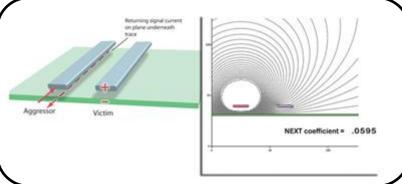

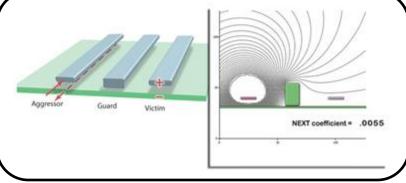

### Crosstalk Analysis

- 주변 신호선과의 Noise Coupling 현상 해석

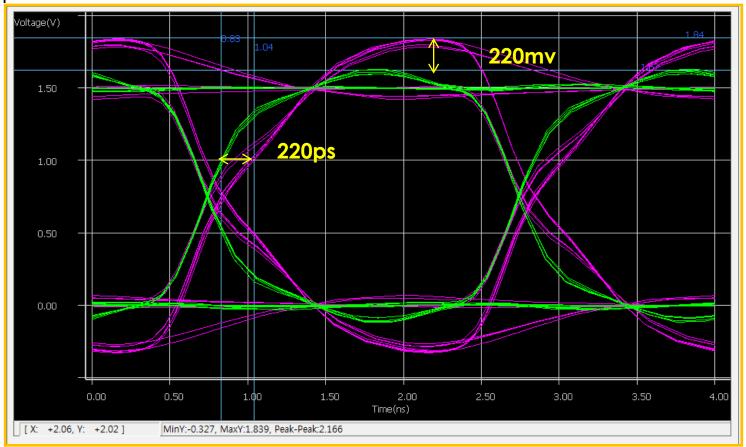

#### Noise Margin Issue

#### Timing/Noise Margin Issue

#### Crosstalk Analysis

- 3W

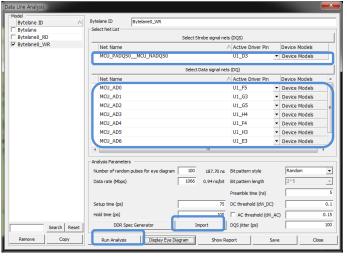

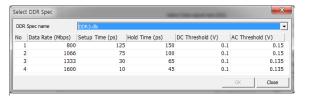

#### Data Line Analysis

- DDR Data Line의 Byte별 Analysis 일괄 수행.

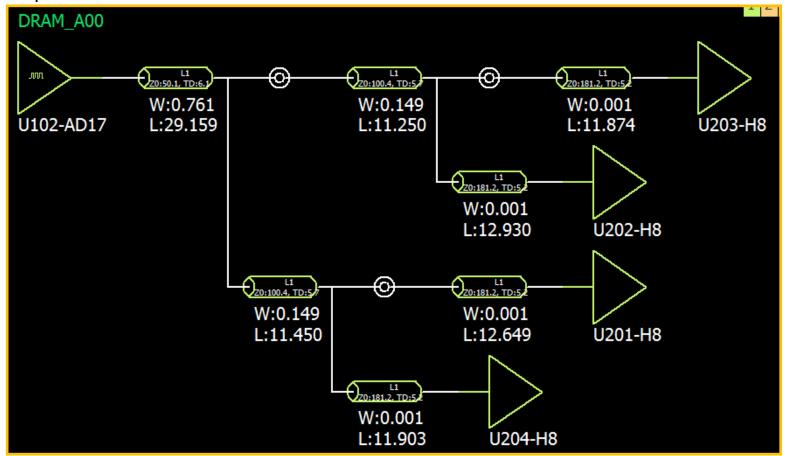

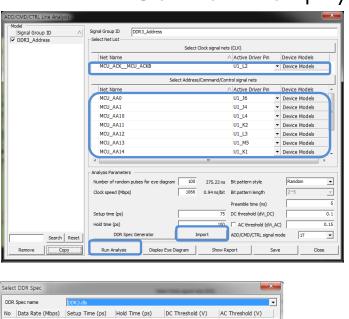

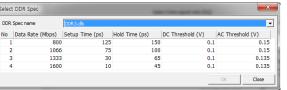

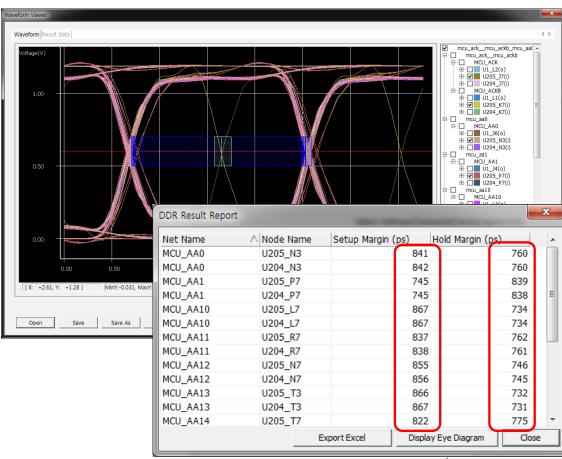

### **◆** ADD/CMD/CNTR Line Analysis

- DDR Control Line의 Byte별 Analysis 일괄 수행.

### ◆ Timing/Noise Margin Analysis

- Margin = Reflection + SSN + Crosstalk + Jitter

### ◆ Read Timing Budget 예 (DDR2-667 사례)

\_

| PCB/Interconnect Skew Component                | Setup | Hold | Units | Comments                                                                                                           |

|------------------------------------------------|-------|------|-------|--------------------------------------------------------------------------------------------------------------------|

| Crosstalk                                      | 40    | 40   | ps    | -                                                                                                                  |

| Data Group Trace Mismatch                      | 15    | 15   | ps    | - M/S: 7.1ps/mm, S/L:5.5ps/mm                                                                                      |

| SSN                                            | 80    | 80   | ps    | - Power Trace 구조                                                                                                   |

| Termination Mismatch(VOH/VOL)                  | 15    | 15   | ps    | Termination mismatch error that reduces the input eye. (OCD calibration 필수)                                        |

| Eye Reduction                                  | 50    | 50   | ps    | $\rm V_{REF}$ mismatch error, termination error, and eye reduction due to slew rate differences between DQS and DQ |

| Jitter                                         | 100   | 100  | ps    | 온도, 전압, Corner Chip                                                                                                |

| Total Board Skew                               | 300   | 300  | ps    | -                                                                                                                  |

| DRAM output skew(tDQSQmax)                     | 240   | 240  | ps    | From DDR2-400/533/667/800 data sheet (350/300/240/200)                                                             |

|                                                |       |      |       |                                                                                                                    |

| DDR controller input skew requirement(tDISKEW) | 550   | 550  | ps    | Controller Spec.                                                                                                   |

| Read Timing Margin                             | 10    | 10   | ps    | Margin = Controller Requirement – DRAM – Board Skew (DRAM out + Board Skew < Controller Requirement )              |

### ◆ Write Timing Budget 예 (DDR2-667 사례)

\_

| PCB/Interconnect Skew Component             | Setup | Hold | Units | Comments                                                                                                                                  |

|---------------------------------------------|-------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Crosstalk                                   | 40    | 40   | ps    | -                                                                                                                                         |

| Data Group Trace Mismatch                   | 15    | 15   | ps    | - M/S: 7.1ps/mm, S/L:5.5ps/mm                                                                                                             |

| SSN                                         | 80    | 80   | ps    | - Power Trace 구조                                                                                                                          |

| Termination Mismatch(VOH/VOL)               | 15    | 15   | ps    | Termination Mismatch Error that reduces the input eye. (OCD calibration $\mathbb{H}^+$ )                                                  |

| Eye Reduction                               | 50    | 50   | ps    | $\ensuremath{\text{V}_{\text{REF}}}$ mismatch error, termination error, and eye reduction due to slew rate differences between DQS and DQ |

| Jitter                                      | 100   | 100  | ps    | 온도, 전압, Corner Chip                                                                                                                       |

| Total Board Skew                            | 300   | 300  | ps    | -                                                                                                                                         |

| DDR Controller output skew(tDQSQmax)        | 290   | 290  | ps    | DDR Controller Spec.                                                                                                                      |

| DDR controller Output setup/hold            | 750   | 750  | ps    | Assumes Center Align                                                                                                                      |

|                                             |       |      |       |                                                                                                                                           |

| DRAM Input setup/hold (tDS/tDH) Requirement | 100   | 175  | ps    | From DDR2 data sheet(400/533/667/800)<br>(150-275/100-225/100-175/50-125)                                                                 |

| Write Timing Margin                         | 60    | -15  | ps    | Margin = DDR controller – DRAM Requirement – DDR controller skew - Board Skew (Controller Output - Board Skew > DRAM Requirement)         |

### Margin distribution policy

- Do not have blind faith in a Design Guide from Vendor.

- Termination required

- Net spacing: 3W

- Appropriate Decoupling Capacitor

- No termination(Except Clock)

- Net spacing: 2W

- Tight length matching

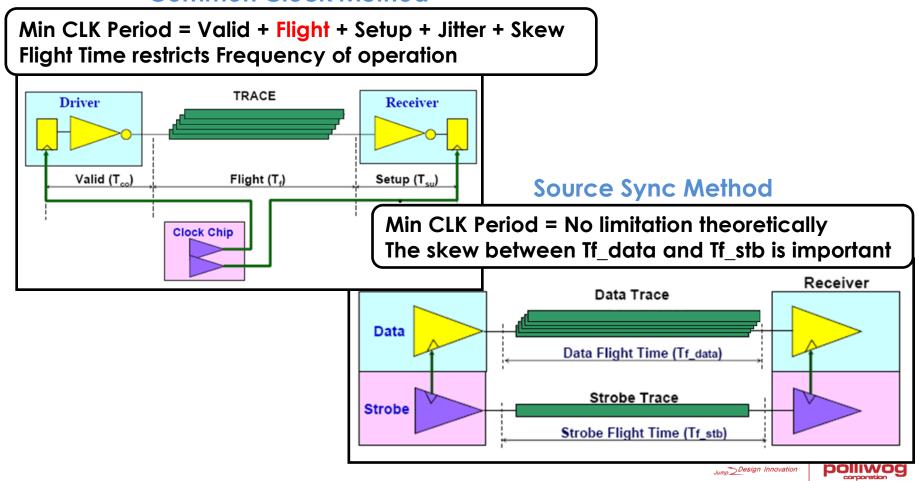

#### Data Transfer Method

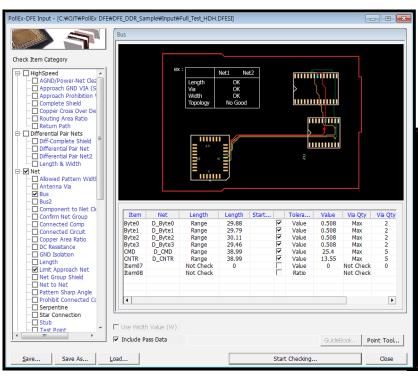

#### **♦** BUS

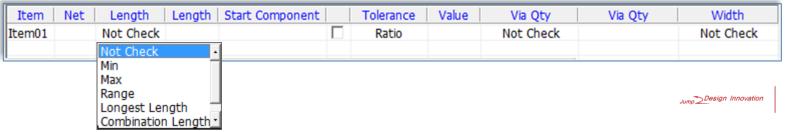

#### **Check Items:**

- Trace length matching with tolerance.

- Via quantity.

- Trace width.

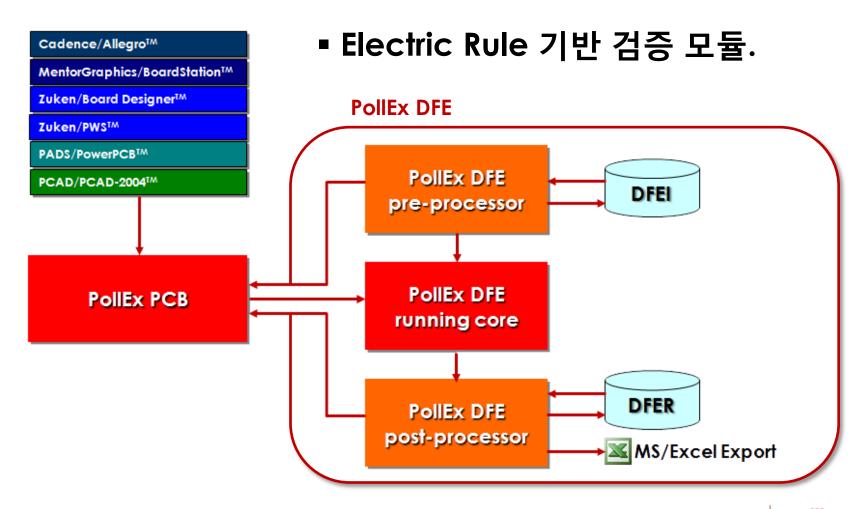

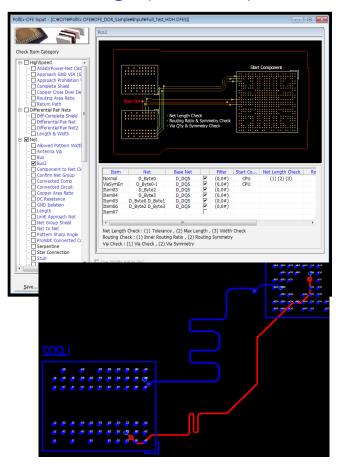

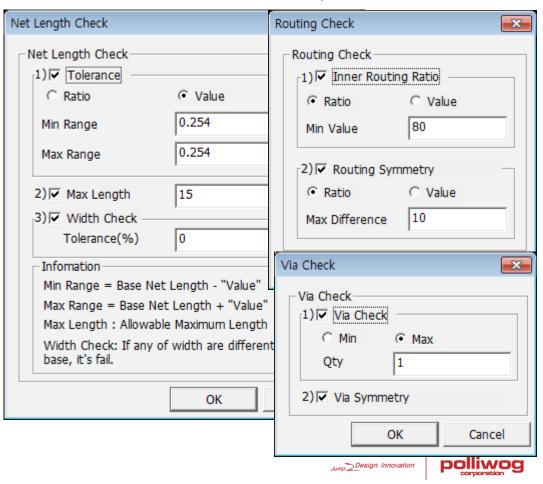

### **PoliEx DFE**

#### ♦ BUS2

- Routing symmetry between strobe and data is Key.

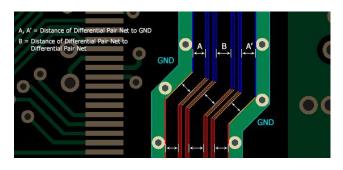

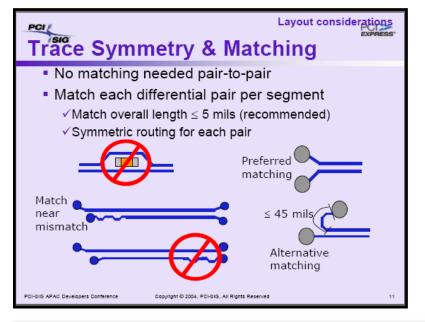

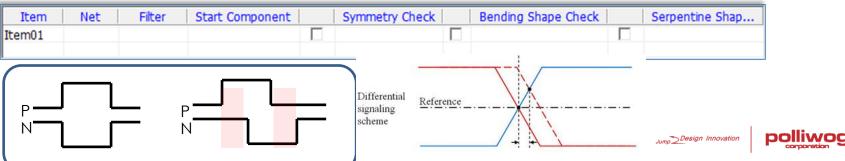

#### Differential Signalling

- Length matching between P/N signals.

| Item   | Net   | Start Comp     | End Comp | Filter |    | Toleran  |           |   | Segment Distance |                 |     | TP TF      | Distance |           | e Anti-Pad | Except Layer |

|--------|-------|----------------|----------|--------|----|----------|-----------|---|------------------|-----------------|-----|------------|----------|-----------|------------|--------------|

| Item01 |       |                |          |        |    |          | 80        |   | Minimum Distance | e 0             |     |            |          | Not       | Check      |              |

| Item   | Net 0 | Group   Filter | GND Net  | Group  | Pi | n Escape | Via Escap | e | Net Clearance    | Shield Distance | - T | olerance(% | )   Show | Segment . |            |              |

| Item01 |       |                |          |        |    |          |           |   |                  |                 |     |            |          |           |            |              |

|        |       |                |          |        |    |          |           |   |                  |                 |     |            |          |           |            |              |

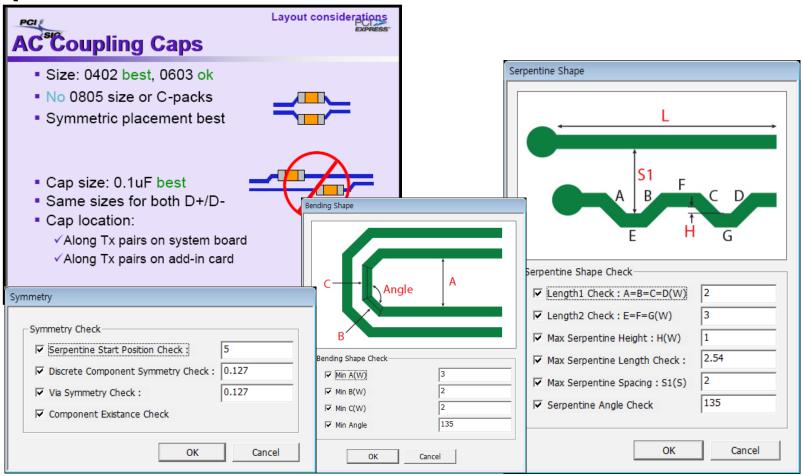

### **PoliEx DFE**

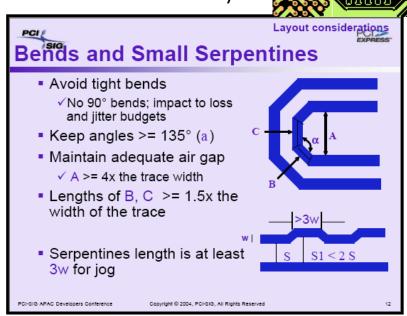

#### Serpentine

- Routing symmetry between strobe and data is Key.

#### Serpentine

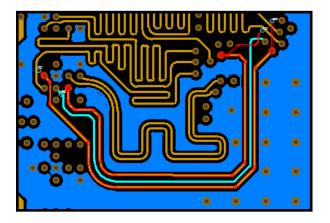

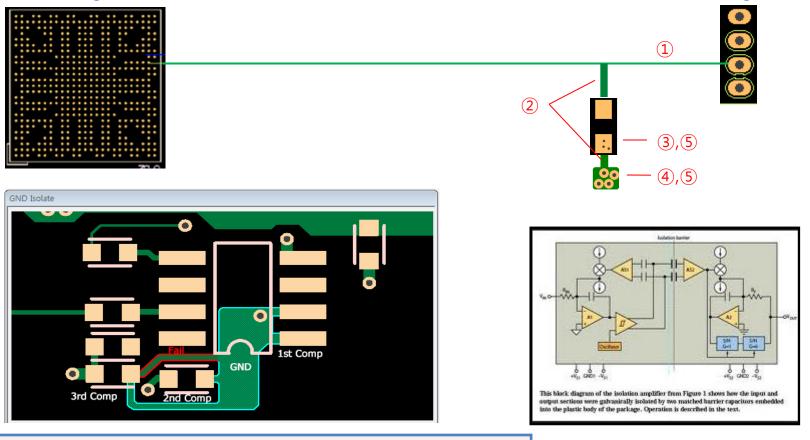

#### Ground Barrier Effect

- Audio signal needs ground barrier in order to prevent noise coupling

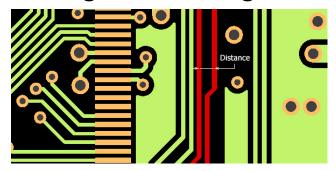

### **PoliEx DFE**

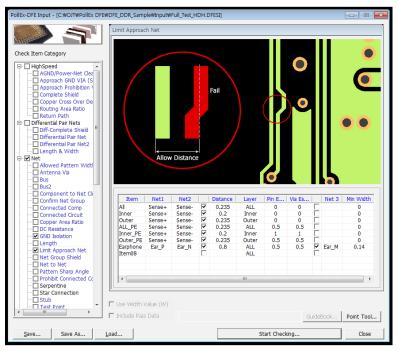

### Limit Approach Net

#### **Check Items:**

- Separation between Net1 and Net2.

- Ground barrier existence.

- Ground barrier minimum width.

| Item   | Net1 | Net2 | Distance | Layer | Pin Escape | Via Escape | Net 3 | Min Width |

|--------|------|------|----------|-------|------------|------------|-------|-----------|

| Item01 |      |      |          | ALL   |            |            |       |           |

|        |      |      |          |       |            |            |       |           |

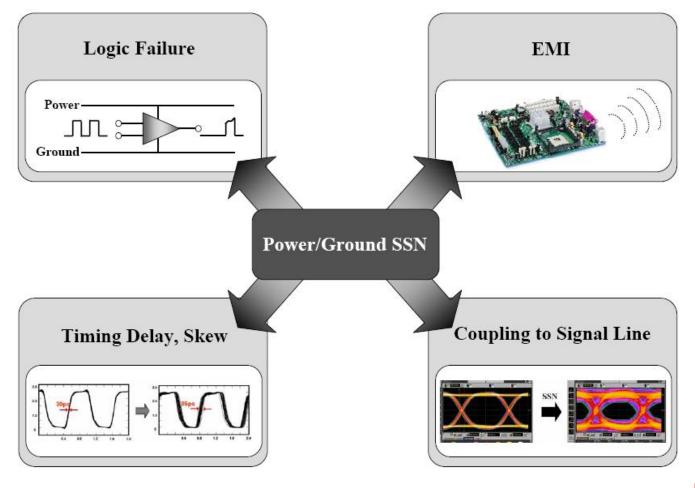

### **♦** Power Integrity

- Power/Ground Bounce, SSN/SSO Voltage drop Power drop Noise  $\Delta V$ di Timing push-out Resultant waveform V=NLeff seen at the end of a net die Ground bounce Noise VRM Time Leff (Lead) Chip Display Panel Leff (Trace) Driver IC Control IC Ground -Power Supply Memory **GND**

#### Problems by Power/Ground SSN

## **PoliEx DFE**

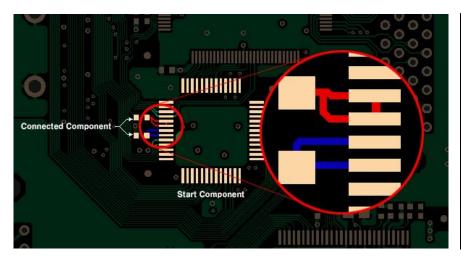

#### **♦ Star Connection**

- In case of sharing one capacitor, connection should be isolated.

| Item   | Star Component | Connected Component | Check Net |

|--------|----------------|---------------------|-----------|

| Item01 |                |                     |           |

|        |                |                     |           |

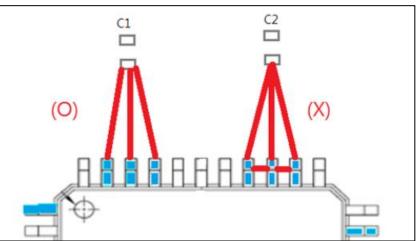

#### GND Isolation

- ESD discharge path should be isolated and direct connect to main ground.

| Item   | Check Pins | MGND-Count | GND Isolation | Via Location | Distance |

|--------|------------|------------|---------------|--------------|----------|

| Item01 |            |            |               |              |          |

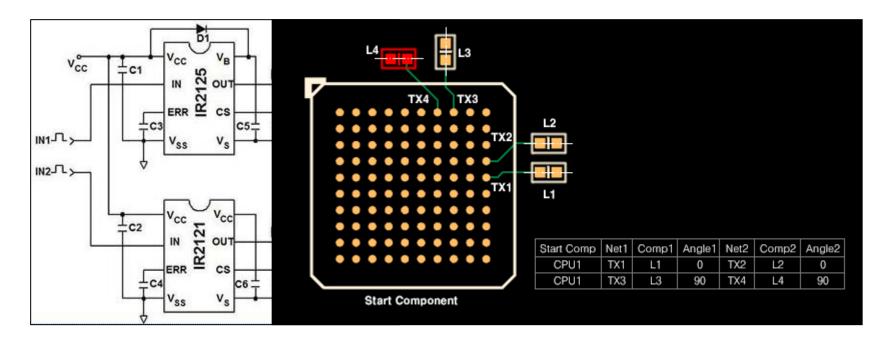

#### **♦** Component Direction

- Check passive devices' placement angles.

| Item   | Start Component | Angle | Net1 | Comp1 | Net2 | Comp2 |

|--------|-----------------|-------|------|-------|------|-------|

| Item01 |                 |       |      |       |      |       |

|        |                 |       |      |       |      |       |

### **PoliEx DFE**

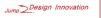

Expectation for PollEx DFE

Consider engineering faults in early design stages.

- → Accumulate Knowledge for Engineering.

- → Save Time-Consuming Cost. (Time to Market)

- → Get Superior Competitive Power to Competitors.

# Thank You!

www.polliwogeda.com