삼성전자, 16GB HBM2E 메모리로 HPC 시장 공략

기사입력 2020.02.04 17:55

1y 16Gb D램 8개 쌓아 16GB 구현

초당 3.2Gb 속도로 410GB 데이터 처리

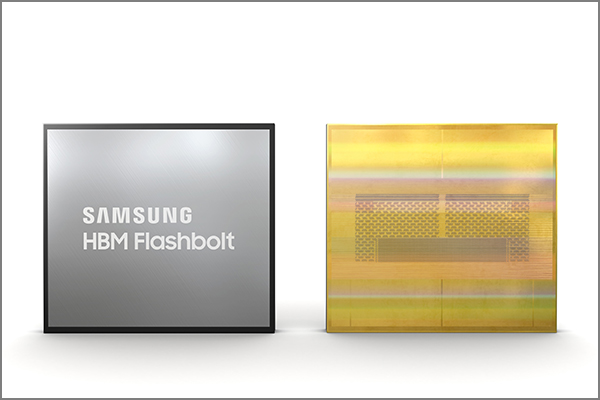

삼성전자는 4일, HPC와 AI 기반 초고속 데이터 분석에 활용될 수 있는 고속 D램, ‘플래시볼트(Flashbolt)’를 출시했다.

▲삼성전자 16GB HBM2E D램 플래시볼트

(사진=삼성전자)

(사진=삼성전자)

플래시볼트는 3세대 16기가바이트(GB) HBM2E(High Bandwidth Memory 2 Extended) D램으로, 2년 전 출시된 2세대 8GB HBM2 D램 ‘아쿠아볼트(Aquabolt)’ 대비 속도와 용량이 각각 1.3배, 2.0배 향상됐다.

플래시볼트는 1개의 버퍼 칩 위에 16기가비트(Gb) 10나노급(1y) D램 칩 8개를 쌓아 16GB의 용량을 구현했다.

삼성전자는 16Gb D램 칩에 5600개 이상의 미세한 구멍을 뚫고 총 4만 개 이상의 TSV(Through Silicon Via) 접합 볼로 8개 칩을 수직 연결한 ‘초고집적 TSV 설계 기술’을 적용했다.

신호 전송 최적화 회로 설계를 활용해 총 1024개의 데이터 전달 통로에서 초당 3.2Gb의 속도로 410GB의 데이터를 처리할 수 있다.

삼성전자는 이 제품을 올해 양산할 계획이다.

한편, SK하이닉스는 지난 8월, HBM2E D램 개발에 성공했다고 밝혔다.

이수민 기자

많이 본 뉴스

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com

.jpg)