AI/ML/DL이 반도체 설계와 EDA 툴에 미치는 영향력

기사입력 2019.09.09 12:29

| 멘토, 지멘스 비즈니스, 연례 EDA 포럼 개최

| 사위키 부사장 “ML 성장이 EDA 툴 변화”

| HLS, 반도체 설계 검증의 속도·정확도 높여

머신 러닝, 딥 러닝 그리고 인공지능의 발전이 반도체 설계 시장에도 큰 영향을 끼치고 있다.

멘토, 지멘스 비즈니스가 지난 8월 30일, 서울 잠실 롯데월드 호텔 3층에서 연례 EDA(Electronic Design Automation) 행사인 ‘멘토 포럼(Mentor Forum) 2019’를 개최했다.

▲조셉 사위키 멘토 부사장 (사진=멘토)

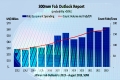

포럼을 위해 방한한 조셉 사위키(Joseph Sawicki) 멘토 IC EDA 부문 수석 부사장은 ‘AI가 반도체 및 EDA에 미치는 영향력(The Impact of AI on Semiconductors and EDA)’라는 주제의 기조연설에서 AI 기반 도메인 특화 아키텍처 제품의 개발이 증가하면서 반도체 설계 산업이 지속 성장할 것으로 전망했다.

사위키 부사장은 “머신 러닝(Machine Leaning; ML) 기반의 반도체 설계를 위한 벤처 캐피탈의 투자가 증가하고 있다”라며, “ML 시장이 성장하면서 EDA 툴도 많은 기회를 얻고 있다”라고 말하며, 도메인 특화 아키텍처로서 AI와 ML 분야를 언급했다. 그리고 에지 애플리케이션에 최적화된 AI/ML 가속기를 만들 수 있는 새로운 설계 기술의 예로 ‘HLS(High Level Synthesis)’를 들었다.

HLS는 C, C++와 같은 상위수준 프로그래밍 언어를 직접 지원하여 반도체 설계 검증의 속도와 정확도를 높일 수 있는 기술로, 특히 메모리 주변에서 ML에 중요한 아키텍처 탐색을 가능하게 한다. 또 높은 성능의 FPGA 시연을 가능하게 하며, ASIC IP를 위한 최적의 전력과 성능, 면적을 전달할 수 있다. 이러한 HLS를 활용한 사례로 엔비디아의 테그라(Tegra) X1-무인자동차를 위한 DNN(Deep Neural Networks)가 소개됐다.

ML 시장의 성장에 따라 EDA 활용분야 역시 확대되고 있다.

▲기조연설을 듣고 있는 엔지니어들 (사진=멘토)

모델을 통해 공정결과를 예측할 수 있는 OPC(Optical Proximity Correction)의 경우, ML의 활용으로 오차 범위 1nm 이내의 결과를 3배 빠른 실행시간으로 가능하게 되었다.

LFD(Litho Friendly Design)는 ML의 활용으로 수율제한요소 예측속도를 10배 개선하였으며, 기존에 발견하지 못했던 새로운 수율제한요소를 발견할 수 있었다.

수율 개선을 위한 DDYA(Diagnosis Driven Yield Analysis) 역시 ML을 통해 수율개선이 가능하다. 노이즈 제거를 통해 수율손실의 원인파악 시간을 단축할 뿐만 아니라 숨겨져 있던 수율제한요소들을 파악하여 수율을 향상시킬 수 있다.

메모리 블록 및 표준 셀과 같이 반복적으로 사용되는 구성 요소를 확인하는데 필요한 수십만 개의 시뮬레이션을 위해서도 ML 편차인식 설계 및 특성화를 활용할 수 있다. 이를 통해 라이브러리 특성화 및 검증 속도의 향상뿐만 아니라 라이브러리 품질 향상과 전력, 성능, 면적(Power, Performance, Area; PPA)을 개선할 수 있다.

AI/ML/DL(Deep Leaning) 설계 알고리즘이 실제 SoC 환경에 최적화 되도록 검증하기 위해서는 하드웨어와 소프트웨어를 동시에 가동 및 가속할 수 있는 에뮬레이션(Emulation)이 필수다. 멘토의 ‘에뮬레이터 벨로체(Veloce)’는 센서 등의 데이터 역시 가상화 환경을 통해 에뮬레이션할 수 있어 검증을 더욱 가속할 수 있다.

사위키 부사장은 “스마트 시스템이 모든 곳에서 인텔리전스를 주도하고 있으며, AI/ML을 기반으로 특화 IC 설계도 가속화되고 있다”라며, “최첨단 인텔리전스를 구현하려면 시스템 설계 관련 전문 지식과 융합된 IC 혁신이 요구된다”라고 말했다.

그러면서 “멘토, 지멘스 비즈니스는 스마트 IC부터 시스템, 공장 및 도시에 이르기까지 전문 지식을 갖춘 EDA 파트너를 필요로 하는 고객을 지원하는데 적극 나설 것”이라고 밝혔다.

이수민 기자

3D IC-Package 그리고 HDAP 구현을 위한 설계 및 검증 방법

2019-09-17 10:30~11:36

Mentor, a Siemens Business / 김경록 과장

많이 본 뉴스

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com