-

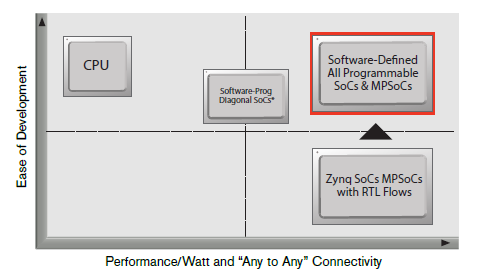

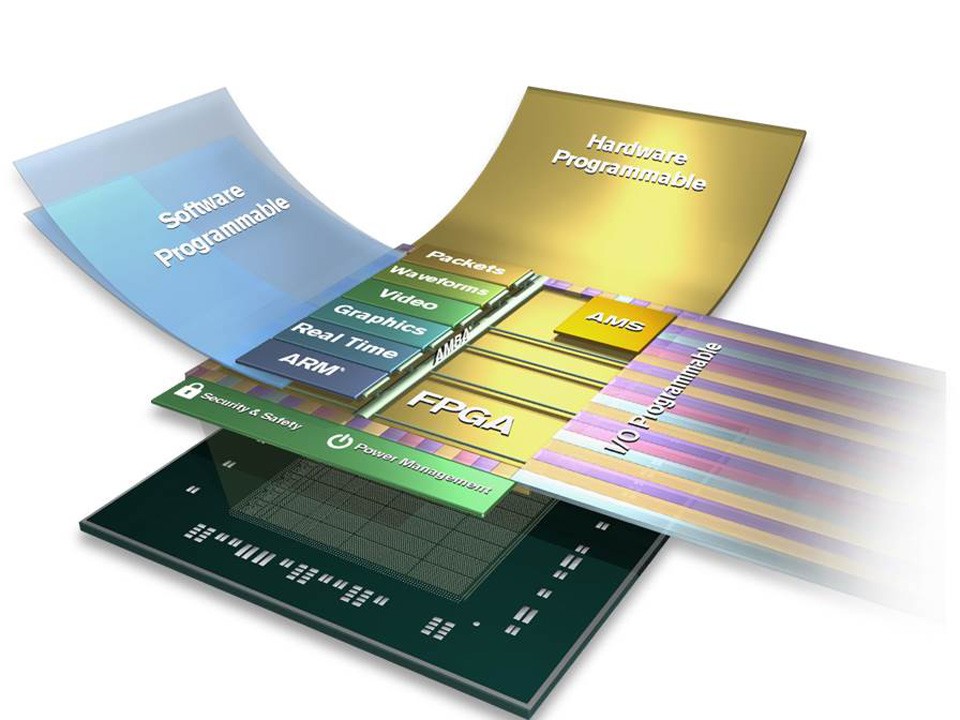

소프트웨어-정의(Software-Defined) 개발 방식, 신..

2016-09-21

-

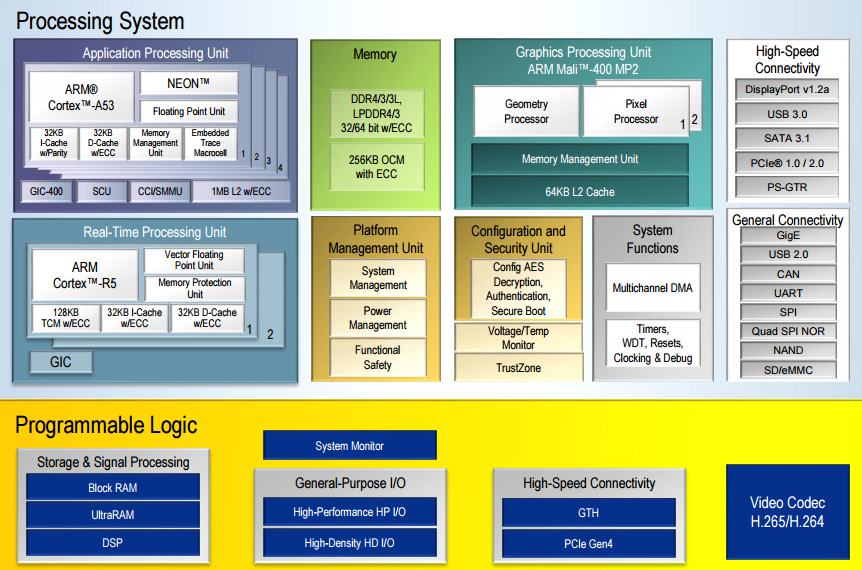

Xilinx, 최신 듀얼코어 디바이스로 징크 울트라스케일+ M..

2016-07-13

-

Xilinx, 안드로이드 오픈 소스 5.1(롤리팝) 운영체제를 ..

2016-07-13

-

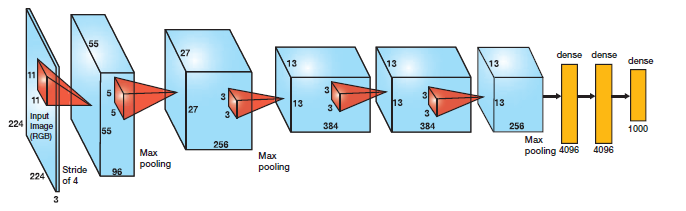

클라우드 머신러닝: FPGA 기반 DNN(Deep Neural ..

2016-07-13

-

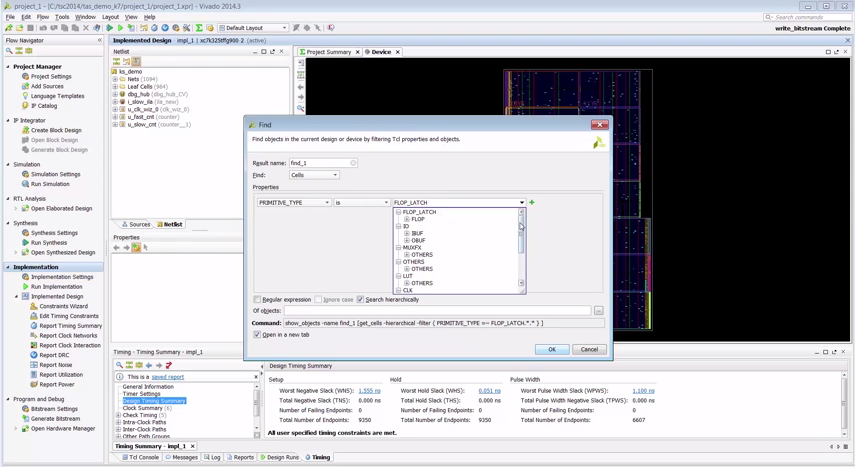

Debugging at Device Startup

2014-11-18

Learn how to use Vivado to debug at and around device startup. You will also learn to use the Trigger at Startup feature introduced in Vivado 2014.1 to configure and pre-arm a debug core and trigger on events at or around device startup. You will learn how to do this from within the Vivado Hardware Manager. There is also no need to re-implement the design. For More Vivado Tutorials please visit:ht..

-

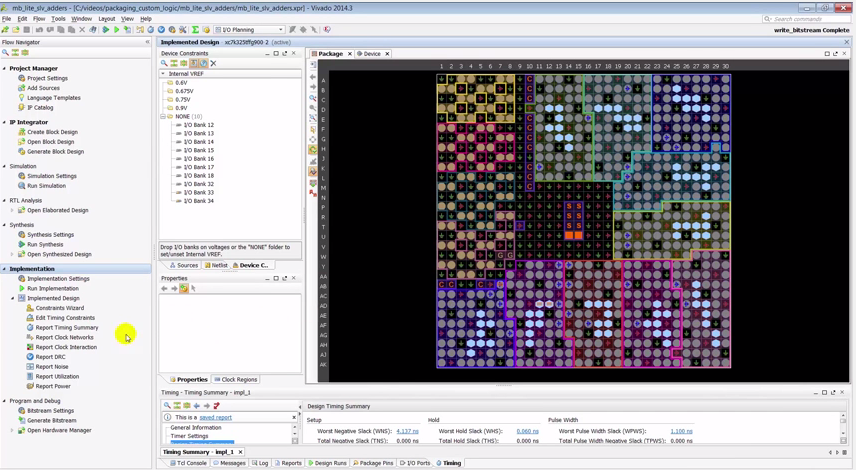

Packaging Custom IP for using in IP Integrator

2014-11-08

Learn how to create an AXI Peripheral using the Create and Package IP function in Vivado and then adds custom logic to the peripheral. The Peripheral is then re-packaged for using in a MicroBlaze based design in IP Integrator and is verified on hardware. For More Vivado Tutorials please visit: http://www.xilinx.com/training/vivado

-

Low Latency 25G/50G Ethernet MAC Connectivity Solution

2014-11-08

This demonstration utilizes two Virtex® UltraScale™ VCU107 boards communicating over four channels of 25G Ethernet through 5 meters of direct attached copper cable and two QSFP+ modules. The low latency 25GE MAC supports the 25G Ethernet Consortium specification.

-

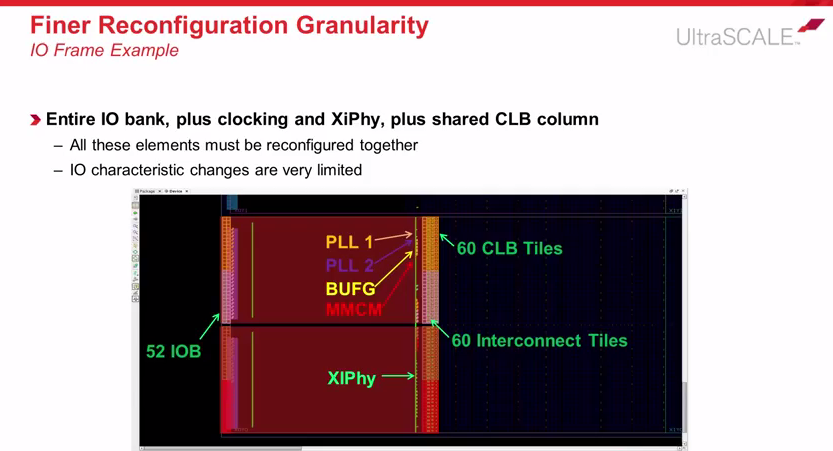

Partial Reconfiguration for UltraScale

2014-11-25

Learn how Xilinx has advanced their groundbreaking Partial Reconfiguration technology in UltraScale devices. This video provides a comprehensive look at new features, expanded capabilities and system requirements for the 20nm UltraScale FPGAs. For More Vivado Tutorials please visit: http://www.xilinx.com/training/vivado

-

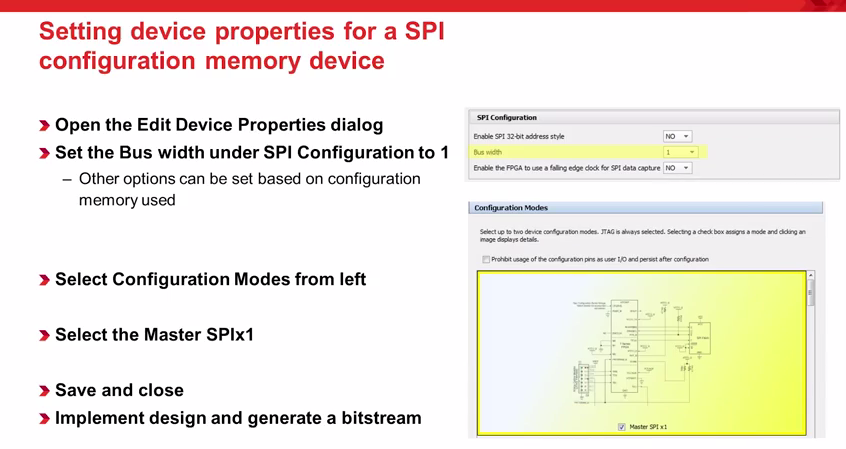

Indirectly Program an FPGA using Vivado Device Programmer

2014-12-02

Learn how to use Vivado Device Programmer to create and configure a configuration memory device. First we will learn how to set the correct bitstream properties and generate a configuration memory file. Then we will take that memory file and use it to program a configuration memory device. Finally we shall use this configuration memory to boot the FPGA. Please note that the "Setting and Editi..

-

Hello World in 5 Minutes on Zynq with Xilinx SDK

2014-12-08

Learn how to create a simple application using the application templates in the Xilinx Software Development Kit (XSDK). We'll walk through the process of creating “Hello, World!”, editing the source code, downloading to the ZC702 development board, and running the Xilinx System Debugger. Additionally, you'll learn how quickly you can start a software development project using t..

-

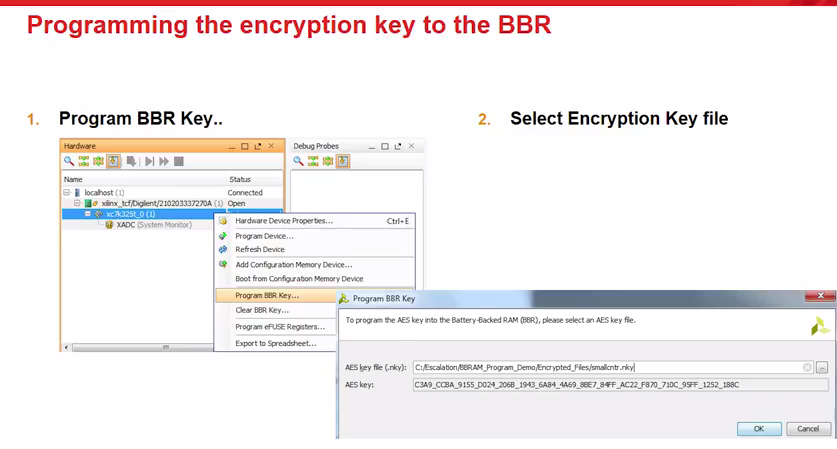

Using Advanced Encryption Standard Keys with the Battery-Backed (BBR) RAM

2014-12-08

Learn how to use Vivado Design Suite to use the advanced encryption standard keys with the battery-backed (BBR) RAM. Please note that the "Setting and Editing Device Properties" is recommended as a pre-requisite to this video. For More Zynq Tutorials please visit:http://www.xilinx.com/training/zynq

-

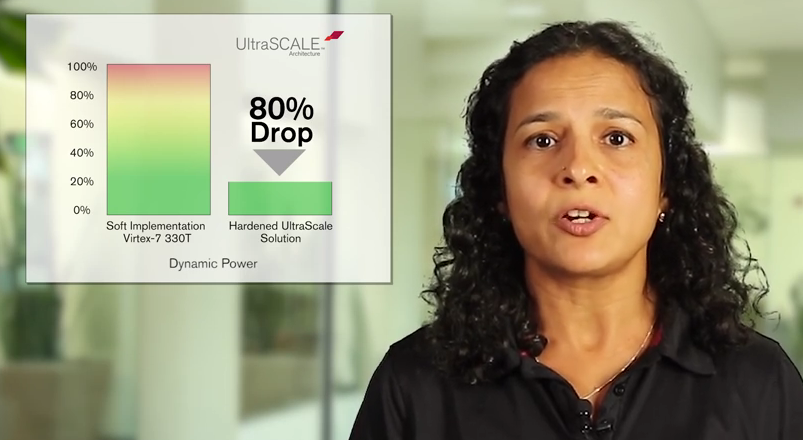

Integrated Interlaken operating at 150 Gb/s in UltraScale FPGAs

2014-12-12

The UltraScale FPGAs now feature integrated Interlaken blocks capable of running up to 150Gb/s over 12 lanes of 12.5Gb/s or 6 lanes of 25Gb/s. This demonstration shows that 150Gb/s operation on a Virtex UltraScale device on the VCU107 evaluation board running in 12x12.5Gb/s mode. By integrating Interlaken, Xilinx is able to reduce, power consumption, logic utilization and design complexity for one..

-

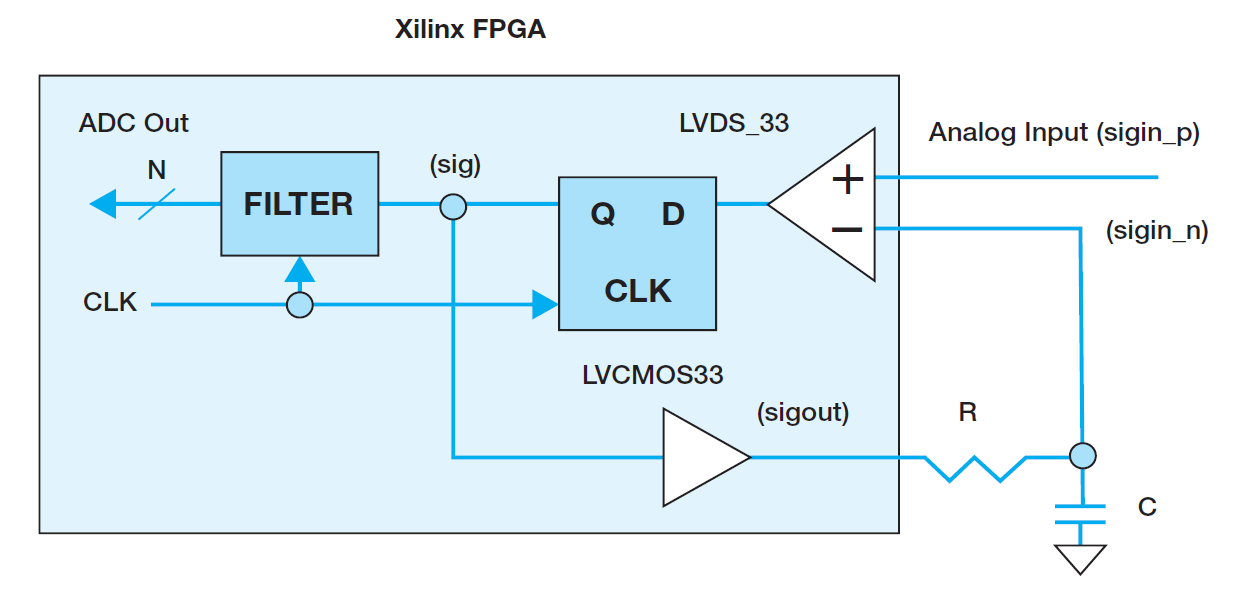

4DSP 백서 - 보다 우수한 빔포밍 성능을 위한 FPGA

2015-03-10

본고(PDF)에서는 Xilinx Virtex-7과 같은 FPGA가 고성능 아날로그 트랜시버와의 조합을 통해 무선 통신 및 RADAR 애플리케이션에서의 빔포밍에 얼마나 이상적인지 설명하고 있습니다. FPGA는 알고리즘 성능을 향상시키고 전력소비를 줄일 수 있는데, 이는 적응형 빔포밍에 사용되는 고속병렬 부동소수점 연산 처리 능력이 우수하기 때문입니다.

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com