-

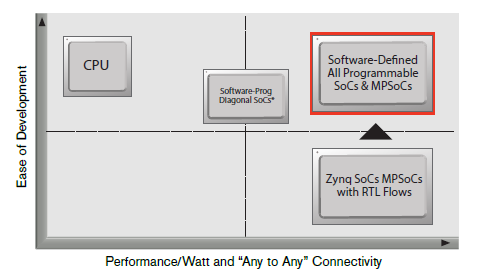

소프트웨어-정의(Software-Defined) 개발 방식, 신..

2016-09-21

-

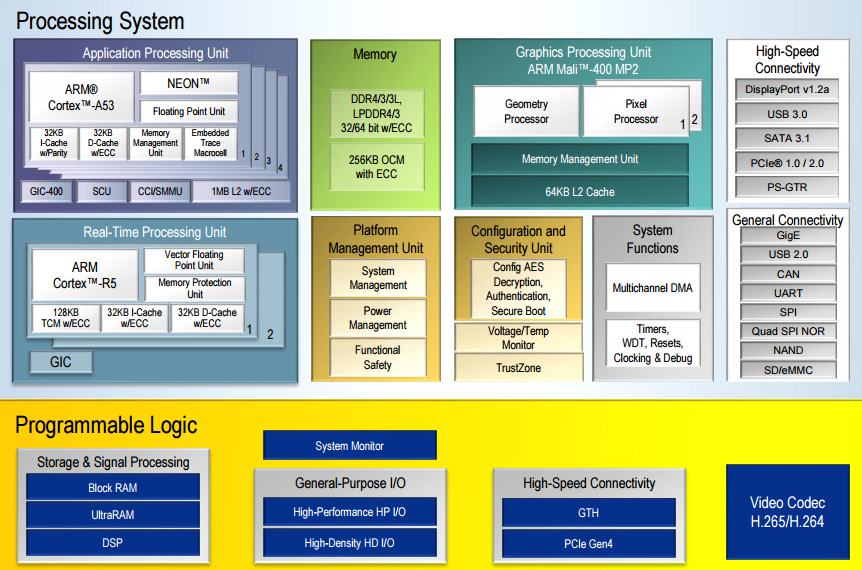

Xilinx, 최신 듀얼코어 디바이스로 징크 울트라스케일+ M..

2016-07-13

-

Xilinx, 안드로이드 오픈 소스 5.1(롤리팝) 운영체제를 ..

2016-07-13

-

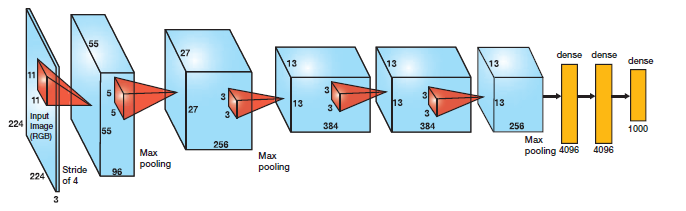

클라우드 머신러닝: FPGA 기반 DNN(Deep Neural ..

2016-07-13

-

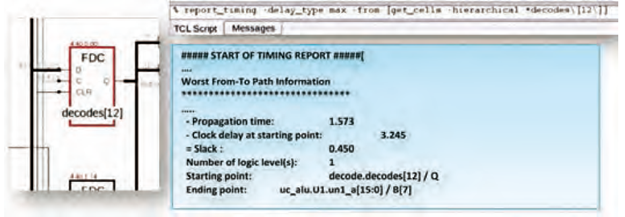

FPGA 디자인, 타이밍 만족이 모든 것!

2014-11-01

툴이나 디자인 기법은 타이밍 성능 목표를 효율적으로 달성하기 위해 존재하는 것이다. 글 / 앤젤라셔튼(Angela Sutton) 제품 마케팅 매니저 (sutton@synopsys.com) 폴 오웬스(Paul Owens) 기업 애플리케이션 엔지니어 (powens@synopsys.com) FPGA 디자인에서 타이밍 성능 목표를 달성하지 못한 경우, 원인을 명확히 밝히는 것은 상당히 어려운 일이다. 솔루션은 타이밍에 부합하도록 디자인을 최적화하기 위한 FPGA 구현 툴의 성능뿐만 아니라, 목표를 미리 규정하고,타이밍 문제를 진단하고 분리하는디자이너의 능력에 따라서 달라지기 때문이다. 디자이너는 클럭을 설정하는데 도움을 주는 특정 팁이나 트릭에액세스할 수 있다. 즉 시놉시스(Synop..

-

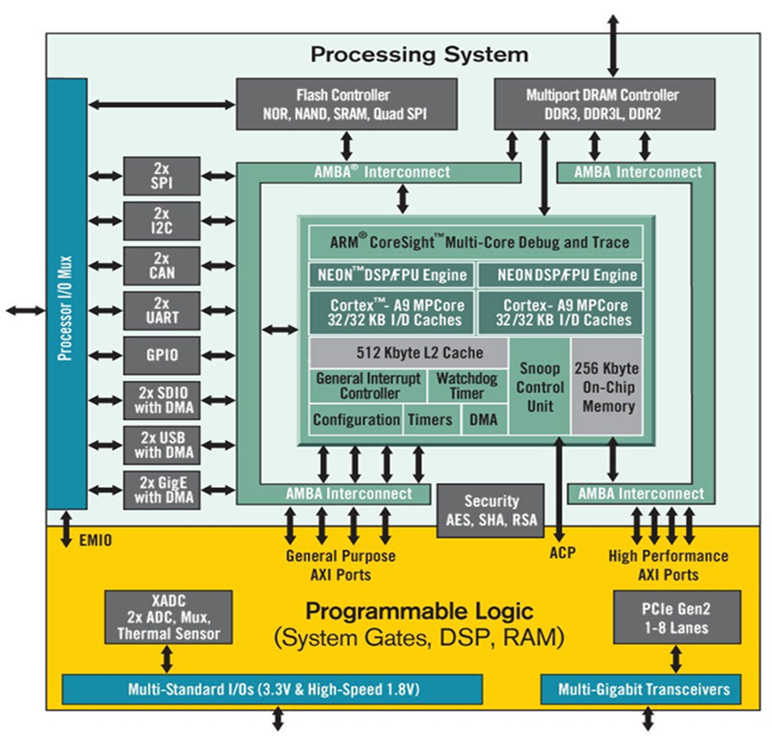

무선 애플리케이션: 징크(Zynq) 올 프로그래머블 SoC를 위한 OS 고찰

2015-01-01

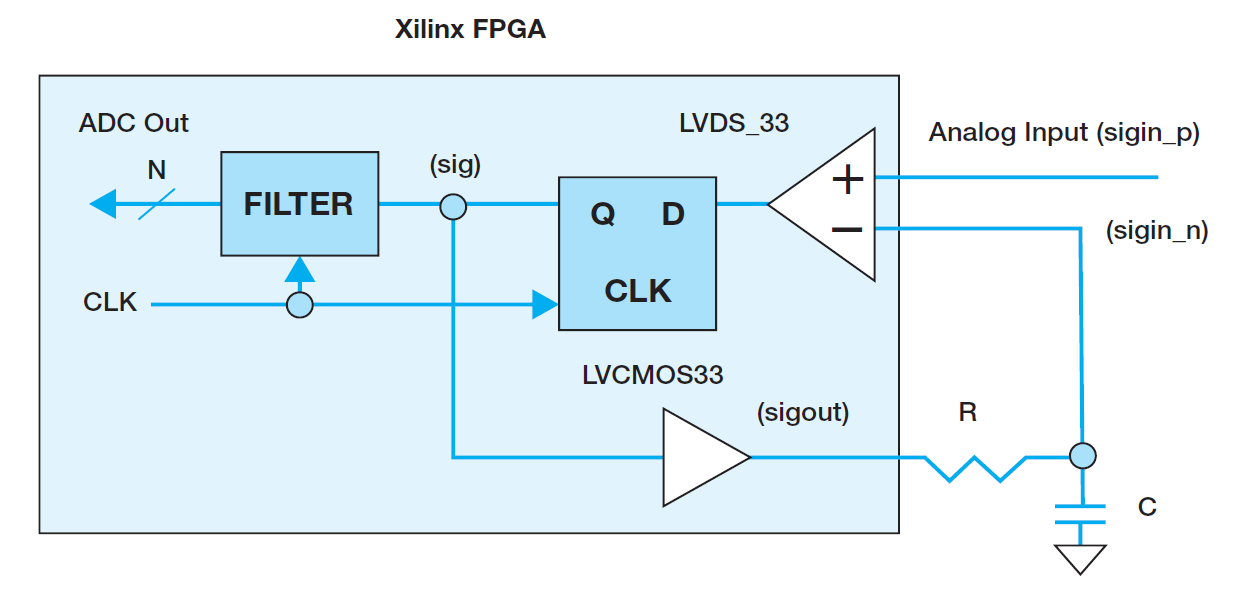

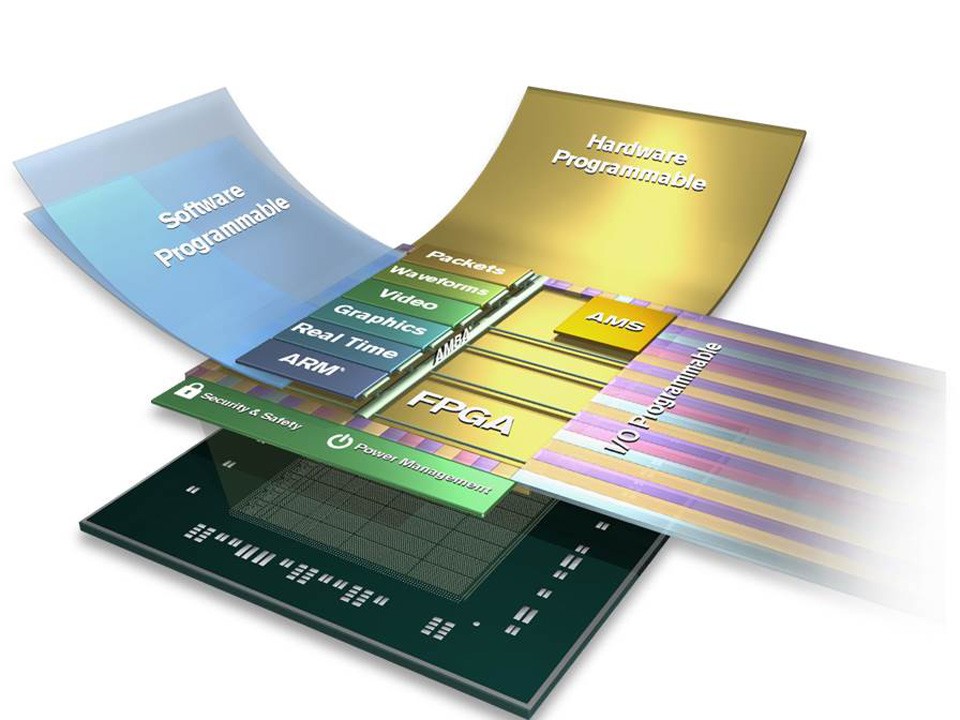

글 / 유안 구 (Yuan Gu) 무선 데이터 처리량이 폭발적으로 증가하면서, 디지털 시그널 프로세싱 기술 및 무선(Radio) 장비에 대한 개선요구가 갈수록 높아지고 있다. 현재 주력은 4G LTE이다. 4G 네트워크는 전세계에 걸쳐 대대적으로 확산되고 있다. 또한 4G 네트워크에 비해 데이터 처리량이 1천배를 넘어설 것으로 예상되는 5G 네트워크에 대한 초기 연구 및 개발작업도 이미 시작되었다. 이러한 최신 기술의 개발은 시스템 벤더들에게 보다 향상된 시스템 통합 및 보다 높은 시스템 성능, 낮은 시스템 BOM 비용, 보다 뛰어난 디자인 유연성, 보다 빠른 시장출시 시간 등과 같은 새롭게 진화된 요건을 제기하고 있다. 전통적인 ASIC 기반 디바이스는 전력 및 비용 목표에 부합하는 ..

-

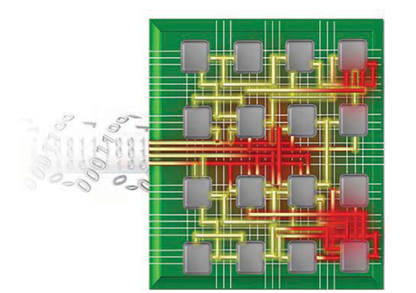

자일링스의 울트라스케일(UltraScale) 아키텍처로 생산성 급등

2015-02-01

자일링스의 울트라스케일(UltraScale) 아키텍처로 생산성 급등 글/ 닉 메타(Nick Mehta), 자일링스 수석 테크니컬 마케팅 매니저 다양한 마켓 및 애플리케이션에서는 상당한 수준의 시스템 대역폭 및 프로세싱 성능 증가가 요구되고 있다. 유선 혹은 무선 통신, 또는 디지털 비디오 및 이미지 프로세싱이든 상관없이 모두 증가하는 데이터 처리량으로 인해 모든 시스템 컴포넌트 상에서 트래픽 및 부담이 증가되고 있다. 따라서 더 많은 데이터들이 병렬 및 직렬 I/O를 통해 온칩 상으로 입력되게 되는데, 이 데이터는 DDR 메모리 형태의 병렬 I/O나 HMC(Hybrid Memory Cube) 및 MoSys 대역폭 엔진과 같은 직렬 메모리 표준 형태의 직렬 I/O를 통해 다시 버퍼링되어야 한다. 그..

-

디자인 시간을 단축시키는 비바도 IPI 및자일링스 IP

2015-04-01

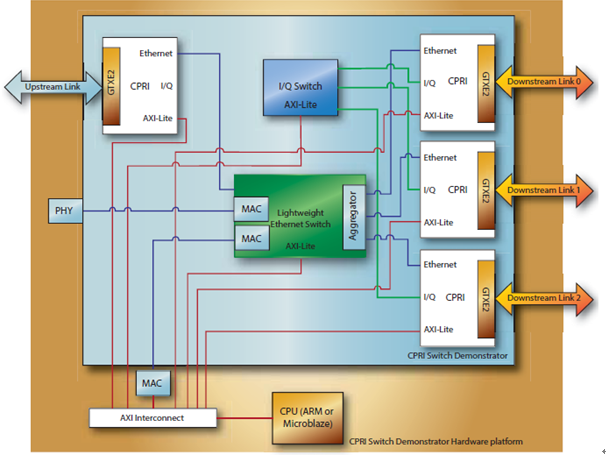

글 : 던컨 콕번(Duncan Cockburn), 자일링스 스태프 디자인 엔지니어 duncan.cockburn@xilinx.com / www.xilinx.com 이글에서는비바도(Vivado) IPI(IP Integrator)를사용해CPRI 원격무선헤드디자인에서어떻게자일링스코어를최적화할수있는지살펴본다. 최신 FPGA-기반 디자인은 다양성 및 수적 측면에서 모두 IP(Intellectual Property) 사용이 갈수록 증가하고 있다. 비바도(Vivado) 디자인 수트의 IPI(IP Integrator) 툴 및 자일링스(Xilinx) 통신 IP는 이러한 IP 블록들을 빠르고 쉽게 연결할 수 있도록 해준다. IPI의 뛰어난 기능을 설명하기 위해 무선 RRH(Remote R..

-

4K TV 개발의간편한해법, 자일링스의징크(Zynq)SoC

2015-03-02

글/ 로저포세트(Roger Fawcett), 옴니텍(OmniTek) 매니징디렉터 해상도 레벨에 따라 4K TV라고도 불리는 UHD (Ultrahigh-Definition) TV는 이미 광범위하게 확산되어 있으며, 4K는 소비자들 사이에서 3D TV 보다 훨씬 더 대중적인 기술로 받아들여지고 있다. 하지만 표준 개발은 뒤처져있다. 4K60 비디오를 지원하는 6Gbps 및 12 Gpbs SDI를 위한 SMPTE(Society of Motion Picture & Television Engineers) 표준 만이 이제 겨우 발표되었고, 동일한 해상도를 지원하는 HDMITM 2.0 및 DisplayPort는 적용 초기 단계에 있다. 4K UHD에 대한 상당한 소비자의 수요를 고려해 볼 때, 수많은 임..

-

SDAccel Development Environment Demonstration

2015-01-08

This video demonstrates the SDAccel development environment for acceleration using a standard X86_64 workstation containing an Alpha data ADM-PCIE-7V3 accelerator.

-

Xilinx at SPS Drives 2014 | SoC-e

2015-01-14

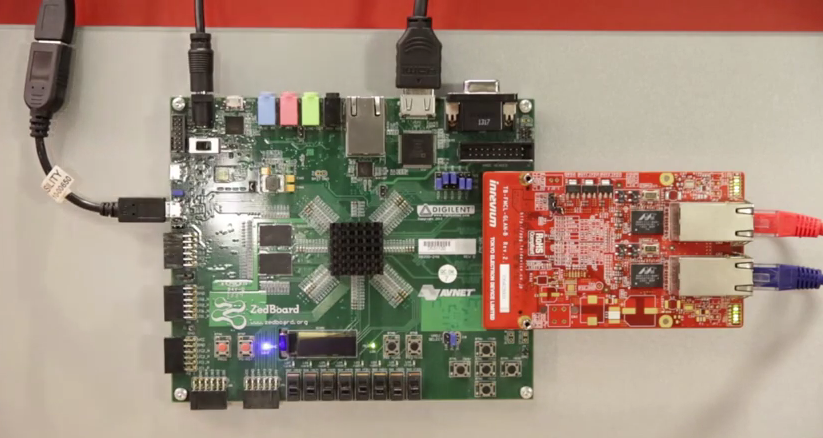

This High Availability Cyber-Physical System demonstration from SoC-e displays zero loss switchover between networks and synchronization between two Netboxes with embedded Bluetooth connectivity for monitoring and maintenance. Xilinx FPGAs and SoCs with IP core solutions from SoC-e provide low latency at low resource consumption with solutions for HSR (High Availability Seamless Ring), PRP (Parall..

-

Xilinx at SPS Drives 2014 | Silicon Software

2015-01-14

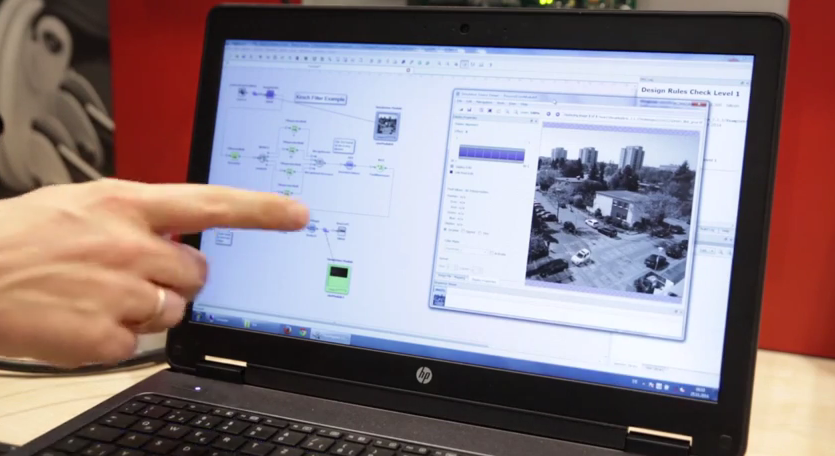

This Embedded Computer Vision for Intelligent Stations demonstration showcases high image processing speed and safe recognition of inspected objects by combining the programmable logic in the Zynq All Programmable SoC with Visual Applets from Silicon Software

-

Xilinx at SPS Drives 2014 | Qdesys

2015-01-14

This Silicon Carbine Multilevel Inverter demonstration from Qdesys showcases a Zynq-7010 All Programmable SoC based three level TNPC implementation with low THD (distortion), high ratio power/volume, three level modulation with very low EMI, low switching loss, and ultra-fast control loops.

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com