-

소프트웨어-정의(Software-Defined) 개발 방식, 신..

2016-09-21

-

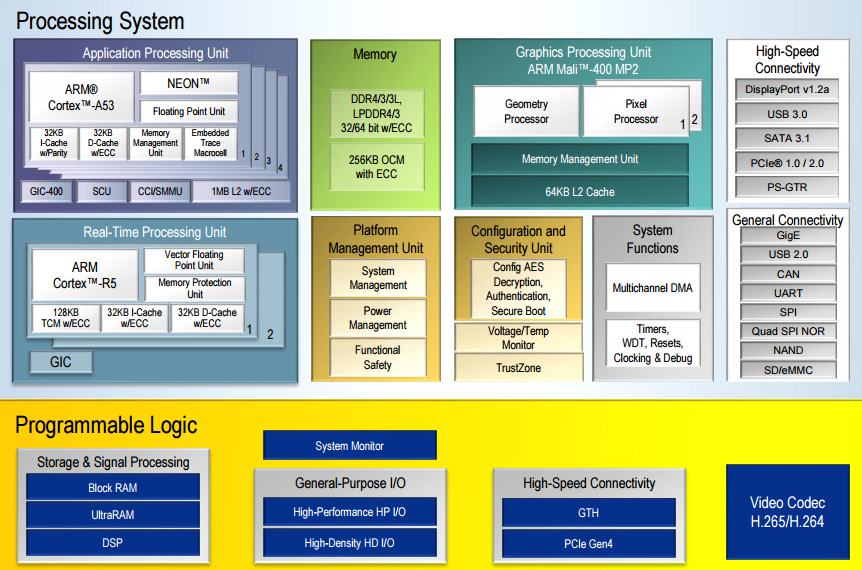

Xilinx, 최신 듀얼코어 디바이스로 징크 울트라스케일+ M..

2016-07-13

-

Xilinx, 안드로이드 오픈 소스 5.1(롤리팝) 운영체제를 ..

2016-07-13

-

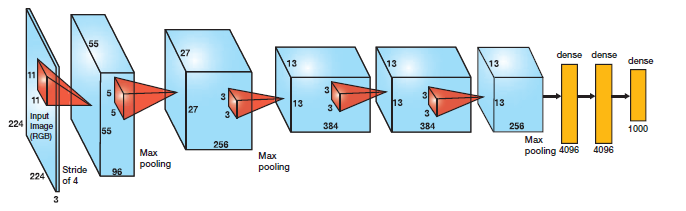

클라우드 머신러닝: FPGA 기반 DNN(Deep Neural ..

2016-07-13

-

[13].gif)

Xilinx, OpenCL, C, C++를 위한 SDAccel 개발 환경으로 크로노스 적합성 달성

2015-01-09

자일링스 코리아 (지사장 안흥식) 2015년 1월 16일 – 자일링스는 OpenCL™, C, C++용 SDAccel™ 개발 환경이 크로노스(Khronos) OpenCL 1.0 표준 적합성 인증을 받았다고 발표했다. OpenCL 표준은 소프트웨어 개발자들이 효율적이고 이식 가능한 코드를 작성하여 자일링스 FPGA에서 다양한 알고리즘을 보다 쉽게 가속시킬 수 있게 균일한 프로그래밍 환경을 제공한다. SDAccel은 SDx™ 제품군의 새로운 제품으로 구조적으로 최적화된 OpenCL, C, C++ 컴파일러가 탑재되어 있으며, CPU/GPU 대비 최대 25배의 향상된 와트당 성능을 제공한다. 또한 다른 FPGA 솔루션보다 3배 이상의 성능 및 리소스 효율성을 자랑한다. ..

-

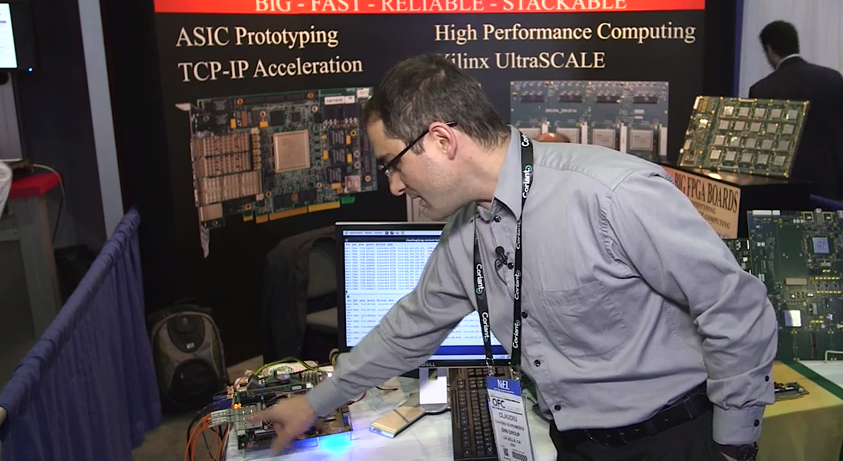

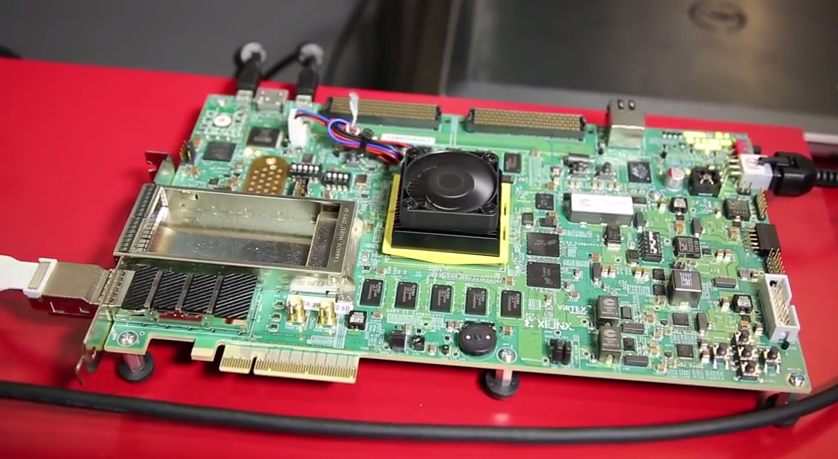

TCP Offload Engine (TOE128) Demonstration featuring the Kintex UltraScale FPGA

2015-04-02

Xilinx Alliance Member The Dini Group demonstrates TCP Offload Engine (TOE128) at OFC 2015 running on Kintex UltraScale FPGA on Dini Group’s PCIe_40G_KU_LL platform for latency sensitive applications.

-

MoSys Bandwidth Engine 2 ICs interfacing with Xilinx UltraScale FPGAs at OFC 2015

2015-04-02

Xilinx Alliance Member demonstration from OFC 2015 highlighting MoSys Bandwidth Engine 2 high-speed serial memory ICs interfacing with Xilinx UltraScale FPGAs.

-

Virtex UltraScale FPGA interoperates with Sumitomo Electric QSFP28 LR4 optics at OFC 2015

2015-04-02

This demonstration featured at OFC 2015 showcases the Virtex UltraScale device with integrated 100G Ethernet MAC driving a Sumitomo LR4 optical module to support a 10km optical link.

-

High density 100G OTN switching solution demo at OFC 2015

2015-04-02

This OFC 2015 demonstration showcases Xilinx’s high-density OTN switching solution featuring the Xilinx Virtex UltraScale VU095 device supporting 2x100G OTN switching applications with an upgrade path to 4/5x100G OTN switching on a larger Virtex UltraScale VU190 device.

-

Virtex UltraScale FPGA interoperates with TE QSFP28 SR4 optics at OFC 2015

2015-04-02

Demonstration from OFC 2015 showcasing the Virtex UltraScale device with integrated 100G Ethernet MAC and the new 100G IEEE 802.3bj RS-FEC IP from Xilinx driving a TE Connectivity QSFP28 SR4 optical module, featuring Coolbit optical engines, to support a 100m optical link.

-

Low latency 4x25G Ethernet MAC solution demo at OFC 2015

2015-04-02

This OFC 2015 demonstration showcases the Virtex UltraScale VCU107 board communicating over four channels of 25G Ethernet through three meters of direct attached copper cable with QSFP28 form factor to Ixia’s Xcellon-Multis QSFP28 100/4x25GE load module. The Xilinx low latency 25G Ethernet MAC supports the 25G Ethernet Consortium specification and will support the future IEEE 25GE specificat..

-

JDSU ONT 400GE test solution featuring Xilinx UltraScale FPGAs

2015-04-06

OFC 2015 demonstration of the JDSU ONT 400GE test solution featuring Xilinx UltraScale FPGAs.

-

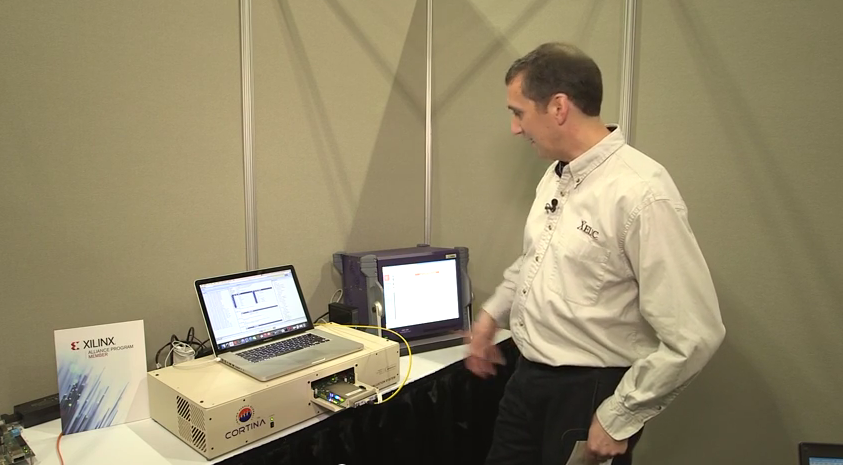

Xelic 100G Staircase EFEC core

2015-04-06

Xilinx Alliance Member demonstration features the new Xelic 100G Staircase EFEC core, compatible with the Cortina 100G staircase FEC and optimized for Xilinx UltraScale FPGAs.

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com