-

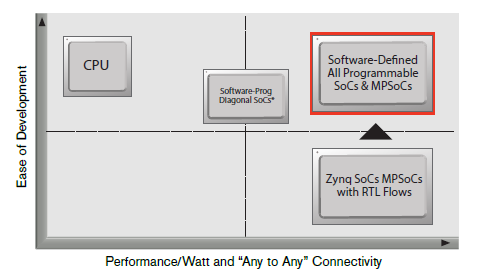

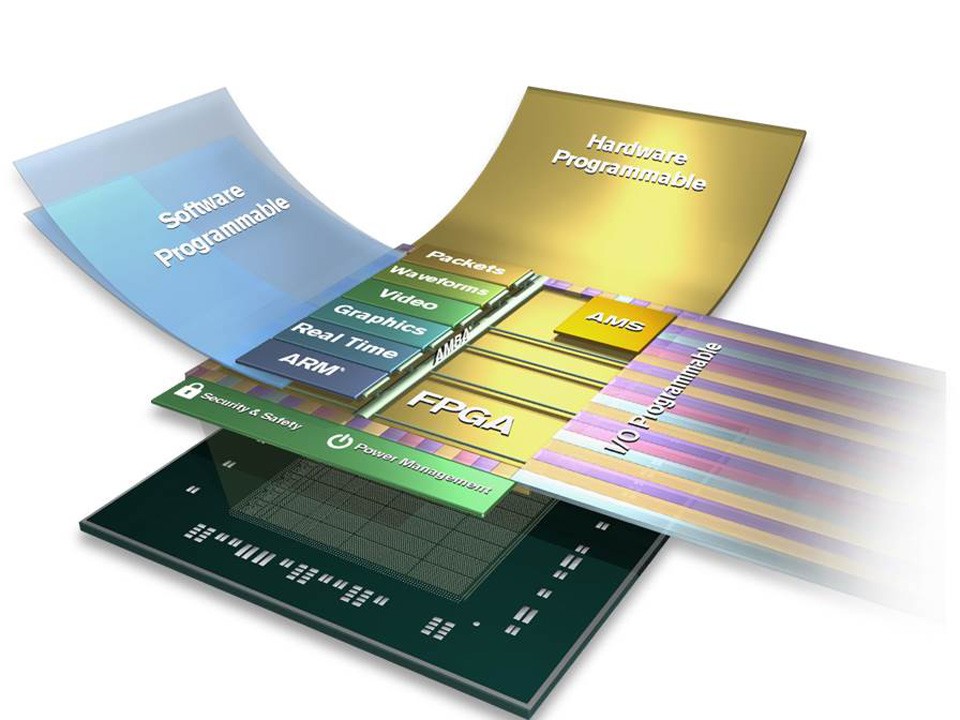

소프트웨어-정의(Software-Defined) 개발 방식, 신..

2016-09-21

-

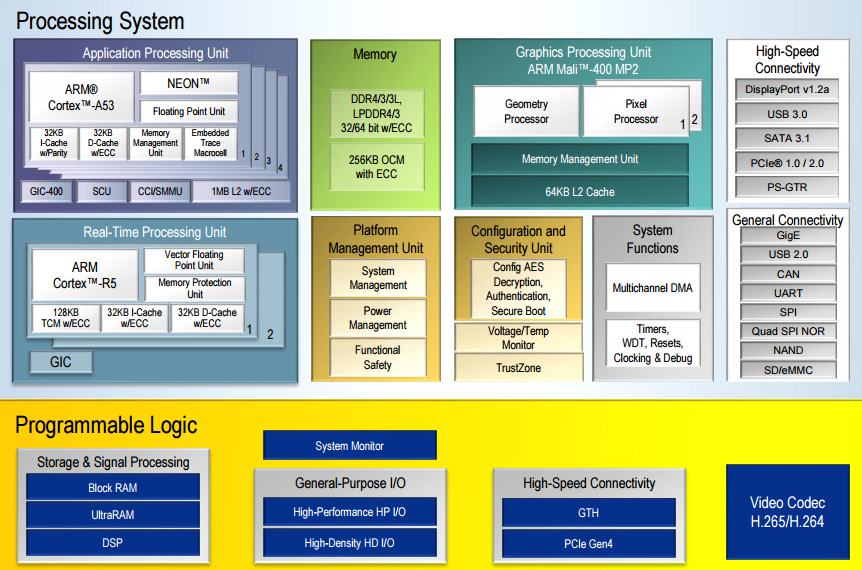

Xilinx, 최신 듀얼코어 디바이스로 징크 울트라스케일+ M..

2016-07-13

-

Xilinx, 안드로이드 오픈 소스 5.1(롤리팝) 운영체제를 ..

2016-07-13

-

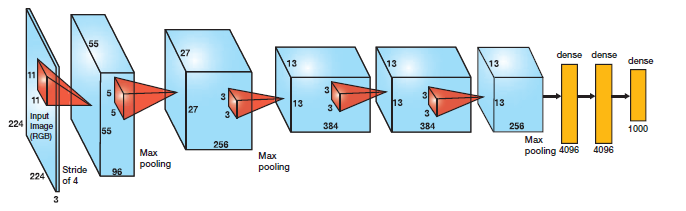

클라우드 머신러닝: FPGA 기반 DNN(Deep Neural ..

2016-07-13

-

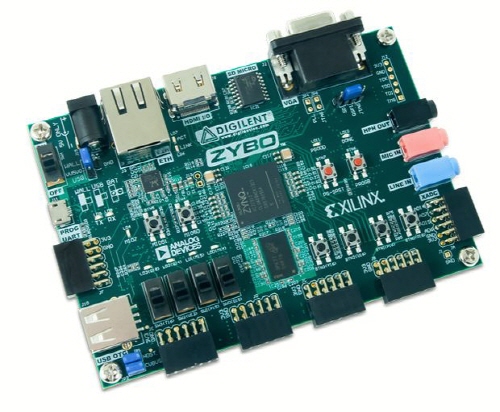

Digilent사의 Zybo와 새로운 Zybot용 Instructables로 즐거움을 만끽하십시오

2015-06-09

Digilent사의 Zybo 보드를 위한 Zybot instructables를 확인해 보십시오. 이 instructables 콜렉션은 귀하의 Zybot을 완전한 기능으로 동작시킬 수 있도록 개발되었으며, 하드웨어, 소프트웨어 및 전력에 있어서 고려해야 할 모든 측면들을 망라하고 있습니다. Zybot Getting Started Guide로 시작하십시오.

-

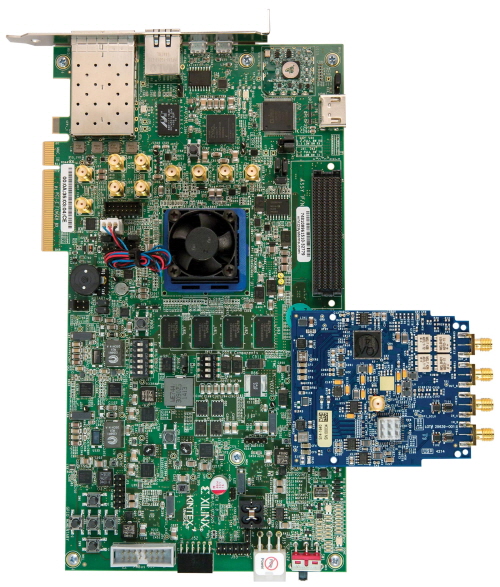

Avnet사가 JESD204B의 고속 아날로그 기능을 갖춘 새로운 Kintex UltraScale FPGA DSP 개발 키트를 소개합니다

2015-06-09

이 새로운 개발 키트는 통신, 의료, 시험계측은 물론 방위 산업과 항공우주 산업에 적합한 광대역 아날로그 데이터 기능을 갖춘 고성능 DSP 애플리케이션의 고속 프로토타이핑을 위한 포괄적인 플랫폼을 제공합니다. 이 시스템에는 Kintex UltraScale XCKU040 FPGA를 탑재한 Kintex® KCU105 평가 보드가 JESD204B 고속 직렬 커넥티비티를 통해 광대역 데이터 수집을 가능케 해주는 Analog Devices사의 AD-FMCDAQ2 고속 아날로그 FMC 카드와 결합되어 있습니다.

-

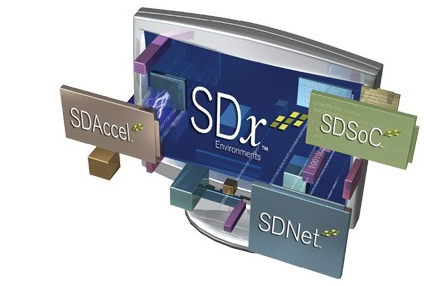

OpenCL, C, C++을 위한 완벽한 개발 환경으로 25배 더 높은 와트당 성능이 가능해진 데이터센터

2015-06-03

자일링스 코리아 (지사장 안흥식) 2015년 5월 27일 – 자일링스는 OpenCL™ 프레임워크, C, C++을 위한 SDAccel™ 개발 환경 2015.1 릴리즈를 발표한다고 밝혔다. SDAccel 개발 환경은 시스템 및 소프트웨어 엔지니어를 위한 SDx™ 제품군의 개발 환경 중 하나로, FPGA를 활용한 데이터센터 애플리케이션 가속에서 최대 25 배의 와트당 성능을 발휘할 수 있다. 이 새로운 릴리즈에서는 SDAccel의 통합 개발 환경(IDE: Integrated Development Environment)을 강화하고, OpenCL 표준 적합성 확장과 플랫폼 및 라이브러리, 디자인 서비스를 제공하는 SDAccel 개발 환경 인증 얼라이언스 회원사들의 에코시스템..

-

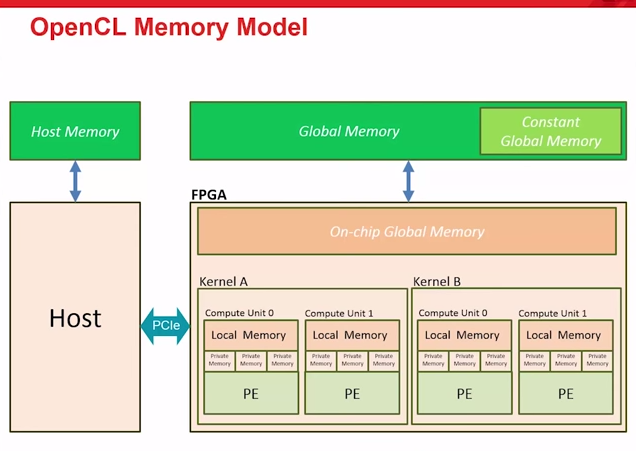

OpenCL Memory Architecture

2015-05-26

OpenCL defines a memory architecture and abstraction model that is common to all computing devices implementing the standard. This means that a programmer only has to learn about 1 memory model, which simplifies application coding. This video provides an overview of the OpenCL memory model and how it is implemented in an FPGA acceleration device.

-

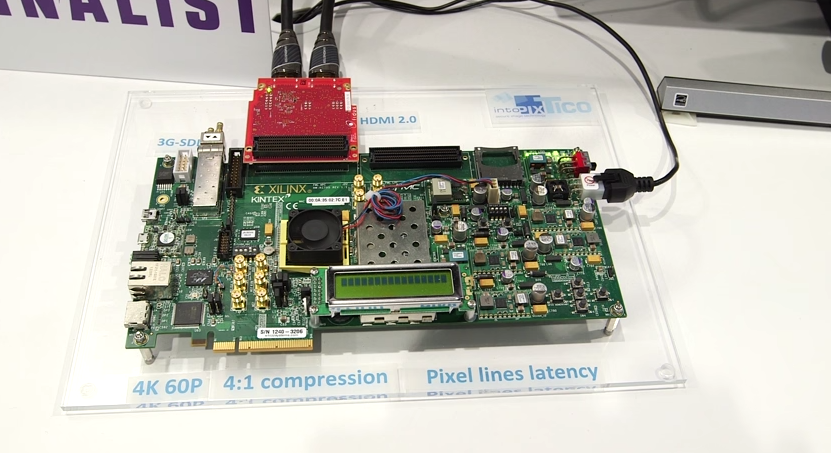

intoPIX TICO

2015-05-21

The intoPIX TICO mezzanine compression provides up to 4:1 visually lossless compression and is demonstrated on the KC705 Kintex-7 evaluation platform using Xilinx HDMI IP cores

-

intoPIX JPEG 2000

2015-05-21

The video demonstrates 10GbE and 4K live video with its JPEG2000 ultra-low latency codec over 1GbE with 10ms of latency from intoPIX.

-

Xilinx, 시스템 검증을 앞당길 수 있는 비바도 디자인 수트 2015.1 발표

2015-05-06

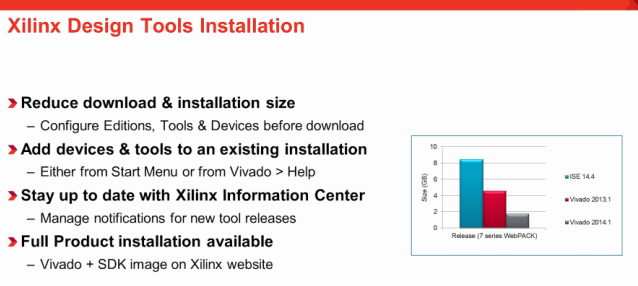

자일링스 코리아 (지사장 안흥식) 2015년 5월 6일 – 자일링스는 시스템 검증을 앞당길 수 있는 비바도® 디자인 수트(Vivado® Design Suite) 2015.1를 발표한다고 밝혔다. 이로써 올 프로그래머블 FPGA와 SoC의 개발 및 배치에 필요한 생산성에서 큰 발전을 이루어낸 셈이다. 이번 릴리즈에는 비바도 랩 에디션과 가속 비바도 시뮬레이터 및 써드파티 시뮬레이션 플로우, 인터랙티브 CDC(Clock Domain Crossing) 분석, 자일링스® SDK(Software Development Kit)와 함께 고급 시스템 성능 분석 등이 포함되어 있다. 새로운 비바도 랩 에디션 비바도 랩 에디션(Vivado Lab Edition)은 비바도 디자..

-

자일링스, 28nm 제품군에서 65% 시장 점유율 달성

2015-05-14

자일링스 코리아 (지사장 안흥식) 2015년 5월 14일 – 자일링스는 28nm 공정 제품군에서 10억 달러 이상의 누적 제품 수익을 달성했다고 밝혔다. 이는 이전 노드보다 3분기 이상 빠른 속도이다. 이와 더불어 자일링스는 2012년 출하된 이후 누적 65%의 28nm 시장 점유율에 달성했다. 계속된 성장으로 자일링스는 2014년, 65%의 28nm 시장 점유율을 기록했으며, 2015년 3월에는 28nm 수익 목표를 초과 달성할 것으로 예상하고 있다. 자일링스의 사장 겸 CEO인 모쉬 가브리엘로브(Moshe Gavrielov)는 “자일링스의 28nm 공정 제품군에서의 성과를 매우 자랑스럽게 생각한다. 10억 달러 이상의 누적 수익의 빠른 상승과 65%의 28nm..

-

NGCodec HEVC Encoder

2015-05-21

This demonstration implements an HEVC encoder running on a KC705 Kintex -7 evaluation platform using the Xilinx HDMI IP cores.

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com