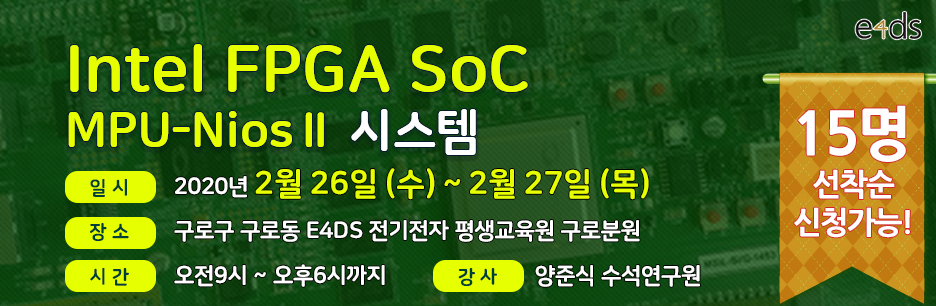

Intel FPGA SoC MPU-Nios II 시스템

본교육은 Verilog에 대해 살펴보고 FPGA 내부구조를 설명하고 Verilog를 통해서 어떻게 동작되는지 이론을 설명하고, Softcore(NiosII)를 사용한 SoC 구현 및 동작 실습을 통해 실무적인 능력을 키우기 위한 교육과정입니다.교육목표

본 과정을 이수함으로써 FPGA 구조와 동작을 이해하고, FPGA의 설정 및 flash에 write하는 방법에 대해 소개합니다. hardware와 software툴을 각각 설명하여 보드를 동작시키고, 여러 다양한 예제를 통해 실제 적용시 고려해야하는 부분에 대해 이해할 수 있습니다.

교육 내용

1. Introduction to IntelFPGA Solutions

2. FPGA structure

3. NiosII processor system hardware development

4. 실습 1

5. Software development and debug tools

6. 실습 2

7. Board bring-up tools

8. NiosII processor custom instructions & component

9. 실습 3

10. Working with IntelFPGA development boards

11. Using NiosII Processors in various applications and multi processor systems

12. 실습 4

실습 보드 :

교육대상

FPGA를 사용하기위해 verilog를 배우고자 하는 학생 또는 직장인.

마감안내

이번 "Intel FPGA SoC MPU-Nios II 시스템" 교육 등록이 마감되었습니다. 많은 관심이 감사드립니다. 신청해주신 분들에게는 필요사항과 교육원 위치에 대한 이메일 및 문자가 개별 발송되오니 참고하시기 바랍니다. 감사합니다.

신청이 마감 되었습니다

| Intel FPGA SoC MPU-Nios II 시스템 | |

| 일정 | 2020-02-26 ~ 2020-02-27 9:00~18:00 |

|---|---|

| 장소 | E4DS 전기 전자 평생 교육원 (구로동 분원) |

| 주최 | E4DS 전기 전자 평생 교육원 |

| 후원 | E4DS 뉴스 |

| 접수인원 | 15명 선착순 결재 접수 마감 |

| 참가비용 | E4DS회원 : 600,000원 비회원 : 660,000원 |

| 안 내 |

본 교육은 E4DS 전기전자 평생교육원에서 진행하는 정규 하드웨어 교육과정입니다. - 효율적인 교육운영상 15명만 지원가능하며, 점심식사가 제공됩니다. - 교육비는 교육일 1주일 전까지만 환불이 가능하며, 이후에는 환불이 안되는점 참고하여 주시기 바랍니다. - 장소 여건상 주차가 지원되지 않으니 대중교통을 이용하여주시기 바랍니다. - 주차시 현금 10,000원 요금이 발생되니 참고하여 주시기 바랍니다. 무통장입금 정보 : 420-084279-01-010 / 기업은행 / 채널5코리아 |

| e4ds 통장사본 다운로드 받기 e4ds 사업자등록증 다운로드 받기 | |

| 시간 | 주제 | 발표자 |

|---|---|---|

| 2020년 2월 26일 수요일 | ||

| 09:00~09:30 | 등록 및 소개 | |

| 09:30~10:30 | 1. Introduction to IntelFPGA Solutions | 양준식 수석연구원 |

| 10:30~11:00 | 2. FPGA structure - FPGA 내부 구조를 설명 하고 verilog를 통해서 어떻게 동작되는지 설명 |

양준식 수석연구원 |

| 11:00~12:30 | 3. NiosII processor system hardware development - System Architecture - Requirements for Nios II Processor Designs - 하드웨어를 디자인하는 방법을 알아본다. |

양준식 수석연구원 |

| 12:30~13:30 | 점심시간 및 휴식 | |

| 13:30~14:30 | 4. 실습-1 | 양준식 수석연구원 |

| 14:30~17:30 | 5. Software development and debug tools - Embedded Design Suite (EDS) - Software Build Tools 등 소프트웨어 개발 시 필요한 툴과 사용 방법을 설명 |

양준식 수석연구원 |

| 17:30~18:30 | 6. 실습-2 - IntelFPGA Quartus : SoC system 합성 및 실습 - Quartus - Hardware 디자인 - 회로도 보는 법 - 핀 할당하는 법 - 소프트웨어 최적화 옵션들 - SBD(Eclipse) - Software Project |

양준식 수석연구원 |

| 2020년 2월 27일 목요일 | ||

| 09:30~11:00 | 7. Board bring-up tools - 보드를 동작시키기 위한 hardware와 software 툴을 각각 설명한다. |

양준식 수석연구원 |

| 11:00~12:30 | 8. NiosII processor custom instructions & component - custom component Integration Into System - 사용자가 필요한 IP를 설계한 후에 이를 시스템에 연결하여 동작시키는 방법을 설명 |

양준식 수석연구원 |

| 12:30~13:30 | 점심식사 및 휴식 | |

| 13:30~14:30 | 9. 실습-3 | 양준식 수석연구원 |

| 14:30~16:30 | 10. Working with IntelFPGA development boards - FPGA의 설정 및 flash에 write 하는 방법에 대한 소개 |

양준식 수석연구원 |

| 16:30~17:30 | 11. Using NiosII Processors in various applications and multi processor systems - 여러 다양한 예제 및 실제 적용시 고려해야하는 부분을 설명한다. |

양준식 수석연구원 |

| 17:30~18:30 | 12. 실습-4 - IntelFPGA Quartus : SoC system 에 custom IP를 추가 및 실습 / Eclipse /Software 실습 및 동작확인 - Quartus - Hardware 디자인 - SBD(Eclipse) - Software Project - interrupt - polling - isr 등록방법 |

양준식 수석연구원 |

양준식 수석연구원

현) XINADIST 수석연구원

IntelFPGA DFAE

현) XINADIST의 FPGA, MCU, AP, Linux 관련 교육 진행 및 각 해당 기술관련 외부자문 및 개발

'intel fpga를 사용한 processor / logic 설계입문 오리지널 마이크로컴퓨터 만들기' 역자

Intel FPGA SoC MPU-Nios II 시스템

1. Introduction to IntelFPGA Solutions

2. FPGA structure

3. NiosII processor system hardware development

4. Software development and debug tools

5. Board bring-up tools

6. NiosII processor custom instructions & component

7. Working with IntelFPGA development boards

8. Using NiosII Processors in various applications and multi processor systems

마감안내

이번 "Intel FPGA SoC MPU-Nios II 시스템" 교육 등록이 마감되었습니다. 많은 관심이 감사드립니다. 신청해주신 분들에게는 필요사항과 교육원 위치에 대한 이메일 및 문자가 개별 발송되오니 참고하시기 바랍니다. 감사합니다.

신청이 마감 되었습니다

위치 안내

E4DS 전기 전자 평생 교육원 (구로동 분원)

구로동 212-1번지 에이스트윈타워 1차 903호- 지하철 이용시 2호선 구로디지털단지역 3번출구 , 7호선 남구로역 1번출구에서 도보로 5분거리

EEWEBINAR

Sponsored Links

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com