자일링스만의 기술적 접근방식으로 CPU, GPU 시장 진입

7nm 최초 도입되는 NoC기술로 데이터 고속화 실현

전통적인 FPGA의 첫 시조라고 봐도 무방한 자일링스의 행보가 심상치 않다.

반도체 ASIC의 에뮬레이터로 시작된 자일링스 FPGA 비즈니스가, 기존 강자들이 점령해 있던 CPU, GPU 시장에, 적응형 가속 기술을 강점으로 하는 플랫폼으로 도전장을 냈다.

AI, 머신러닝 및 빅데이터 처리 등과 같이 빠른 처리를 요구하는 애플리케이션들은 빠른 서버 단의 처리와 효율적인 컴퓨팅 자원 활용이 필수적이다. 이러한 이유로 FPGA가 데이터 센터에 있는 서버에서 CPU와 GPU의 가속화를 돕는 기능으로 많이 사용되었으며, 인텔의 알테라 인수도 기존 X86 서버의 CPU 가속화를 위한 방향으로 사용되고 있다.

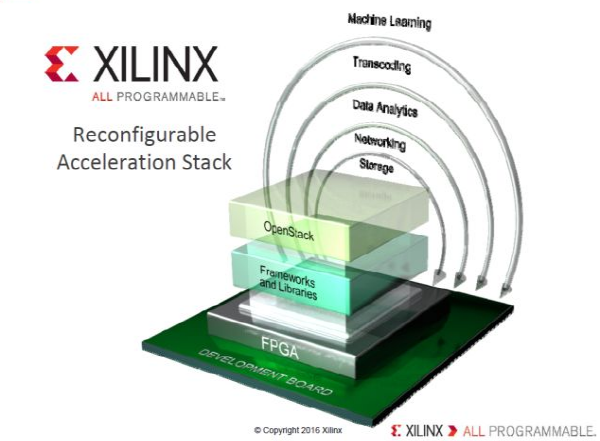

자일링스는 2016년 하이퍼스케일 규모의 데이터 센터를 겨냥한 기술 발표 이후 구글, 마이크로소프트, 아마존 등 대형 인터넷 서비스 업체들과 협업을 하면서 클라우드 애플리케이션을 위한 FPGA로 구동되는 가속 스택 '

reVision'을 통해 기존의 경쟁사 GPU 대비 머신 러닝 추론에서 6배 컴퓨터 비전 처리에서 40배 높은 성능을 보여주었다.

자일링스 FPGA 가속 스택

자일링스 FPGA 가속 스택

4년의 개발과정과 1500명의 엔지니어 투입 그리고 10억 달러의 연구·개발 투자로 만들어낸 이번 ACAP은 데이터센터 사업 접근하는 방식에 있어 새로운 접근법을 보였다.

단순 지원개념의 가속화가 아닌, 제품 자체가 CPU나 GPU의 역할도 하면서, 때에 따라 단순 가속화 지원 역할도 할 수 있는 유연한 독립적 적응형 가속 플랫폼으로 접근한 것이다. 이는 지속적인 프로그래머블 코어 및 여타의 IC 집적 기술과 빠른 데이터 속도를 가능하게 하는 3D IC 적층 기술 개발이 지속 되었기에 가능한 사항이라고 CEO인 빅터 펭은 언급하였다.

무어의 법칙 마지막일지도 모른다는 7nm를 통한 500억 개의 트랜지스터로 구성된 차세대 프로그래머블 로직, 일명 ‘Everest’ FPGA는 무려 기존 CPU 처리속도로 볼 때 10배에서 100배까지 빠른 작업량을 보이며, DNN(Deep Neural Networks) 응용 분야에서는 기존의 16nm 버텍스 VU9P에 비해 20배 이상의 높은 성능을 제공한다.

또한, 'AI 분야에서는 40배의 추론속도, 90배의 분석속도, 100배의 유전체 스피드업을 제공할 수 있으며, 이러한 제품 경험은 클라우드 인프라 스트럭쳐에서 FPGA를 사용한 FaaS 서비스 제공업체를 통해 ACAP 사용 활성화가 될것'이라고 관계자는 전했다.

자일링스가 제공하는 적응형 가속 컴퓨팅 실현 가능 성능

자일링스가 제공하는 적응형 가속 컴퓨팅 실현 가능 성능

5G 원격 무선 헤드는 현재 16nm 울트라스케일+ RFSoC 제품군 대비 4배의 대역폭 지원함으로 매시브-MIMO용 원격 무선 헤드, 밀리미터파 모바일 백홀, 5G 베이스밴드, 고정형 무선 액세스, 케이블용 원격-PHY 노드, 전자전/레이더, 테스트 및 측정, SATCOM, Milcom/Airborne 라디오 및 기타 고성능 RF 애플리케이션까지 혁신적인 효율을 제공할 것으로 보인다.

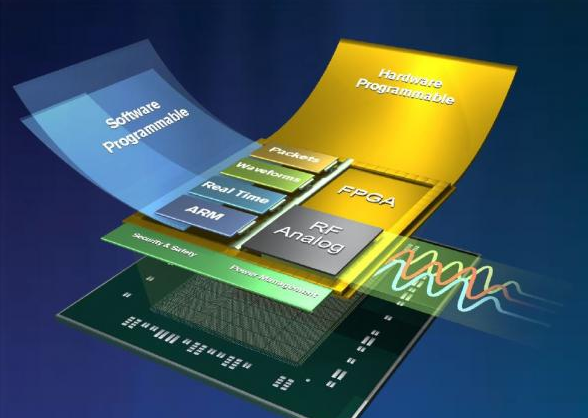

기존 16nm 기반 울트라스케일+ RFSoC 블록다이어그램

기존 16nm 기반 울트라스케일+ RFSoC 블록다이어그램

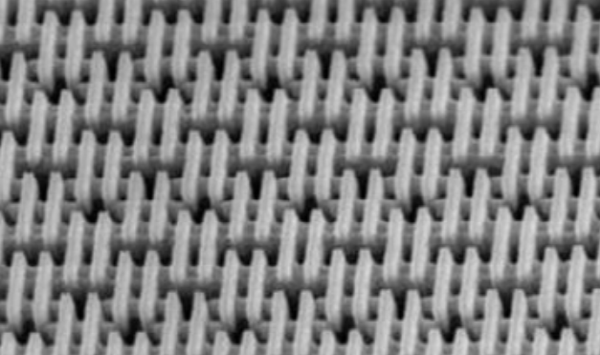

이번에 자일링스에서 발표한 ACAP 포트폴리오는 TSMC의 7nm 제조공정으로 만들어지며, 집적회로 설계의 마지막 단계인 Tape out은 올해 말인 2018년 12월로 예정되어 있다.

TSMC의 7nm 공정을 통한 반도체 확대 모습

TSMC의 7nm 공정을 통한 반도체 확대 모습

자일링스는 이번 ACAP 기반의 프로젝트인 Everest를 위해 총 4년간의 개발과 1,500명의 엔지니어 운용, 그리고 10억 달러 이상의 R&D 비용을 투자하였다고 밝혔다. 특별히 이러한 수치를 밝히는 바에 대해서 한국 자일링스의 안흥식 지사장은 그만큼 큰 사업적 전환과 자일링스의 향후 5년의 방향성을 보여주는 것이라고 언급하며, ACAP은 데이터센터를 중심의 사업영역 확장과 기존 오토모티브, 5G, 오디오와 비디오, 우주 항공분야 및 계측 분야 그리고 요즘 추세인 암호화 기술 분야에도 적용할 것’이라고 밝혔다.

7nm 기반의 ACAP이 적용될 기존 핵심 분야

7nm 기반의 ACAP이 적용될 기존 핵심 분야

자일링스는 500억 개의 트랜지스터를 탑재한 이번 Everest 제품에 관하여 정확히 밝히지는 않았지만 베어다이를 기반으로 한 모놀릭식 및 인터포져 디자인을 혼합하였을 것으로 보인다.

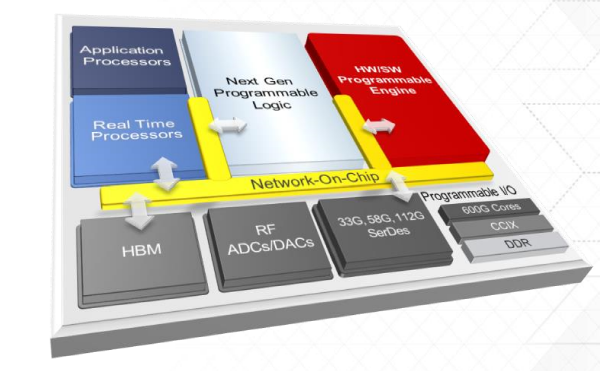

기존 제품보다 빠른 통신 속도를 장점으로 하는 ACAP 블록 다이어그램에는 7nm에 최초의 NoC (Network on Chip) 고속 통신 패브릭을 적용함으로 고속의 빠른 데이터 속도를 보장한다. 이는 CEO인 빅터펭이 밝힌 세 가지 빅 트랜드 중의 하나인 하드웨어가 소프트웨어만큼 민첩하게 반응해야 한다는 생각과 일맥상통한다.

자일링스 CEO 빅터 펭

자일링스 CEO 빅터 펭

NoC (Network on Chip)는 블록다이어그램에 표시된 자일링스의 고성능 차세대 프로그래머블 로직과 애플리케이션 프로세서, 리얼 타임 프로세서, 프로그래머블 엔진, RF, 고속 SerDes, 프로그래머블 IO, HBM까지 고속으로 연결한다. 또한, 적응형 가속 플랫폼의 기본 아이디어인 최적화된 계산 및 적응성을 FPGA의 하드 블록 전용 공간을 통해, 프로그래밍 가능한 실리콘을 남겨 놓는 구조로 운영된다.

7nm에 처음 적용된 멀티코어 고속 데이터전송을 위한 NoC 구조 및 ACAP 블록다이어그램

7nm에 처음 적용된 멀티코어 고속 데이터전송을 위한 NoC 구조 및 ACAP 블록다이어그램

자일링스의 안흥식 지사장은 'ACAP이 CPU와 GPU의 시장을 모두 공략하는 것인가'라는 본지의 질문에 대해 'CPU와 GPU는 범용적 운용이라는 필드를 유지하는 것에 반해, ACAP플랫폼은 유연한 구조를 통해 성능 가속화 기능을 자동으로 적응할 수 있도록 한다'고 하며, '이러한 구조는 고난도의 고속 다중작업을 위한 분야에 적절할 것'이라고 하였다.

대표적 분야로 비디오 트랜스코딩, 데이터베이스 운영, 데이터 압축, 검색, AI를 통한 추론, 유전체학, 머신비젼, 연산 스토리지 및 네트워크 가속화 분야를 언급함으로써, ACAP 이 시장 내 범용 가속기의 카테고리로 자리하고자 함을 표했다.

자일링스 한국의 안흥식 지사장

자일링스 한국의 안흥식 지사장

이번 ACAP 발표에 있어 빅터 펭은 데이터 센터를 가장 성장 잠재력이 큰 부분으로 언급하며, 자일링스의 ACAP 플랫폼을 통해 빠른 업그레이드, 고객 요구 사항 및 제품 포트폴리오의 빠른 발전을 가져올 것이라고 전했다.

현재 자일링스는 ACAP테스트를 위한 소프트웨어를 핵심 고객들에게 제공하고 있으며, 2018년 말 설계를 마무리하고 2019년 중 출하될 것으로 예정하고 있다.