최근 글로벌 빅테크 기업들의 초거대 AI 개발 전쟁이 본격화하고 있다. 이에 더해 초거대 AI가 더 크고 복잡한 모델로 진화할수록 AI 가속기와 메모리 확장 요구는 필연적일 수밖에 없다. 이를 해결하는 CXL(Compute Express Link)는 차세대 인터페이스 기술로 글로벌 대기업들이 앞다퉈 CXL 기술 개발과 생태계 구축에 나서고 있는 상황이다.

.jpg)

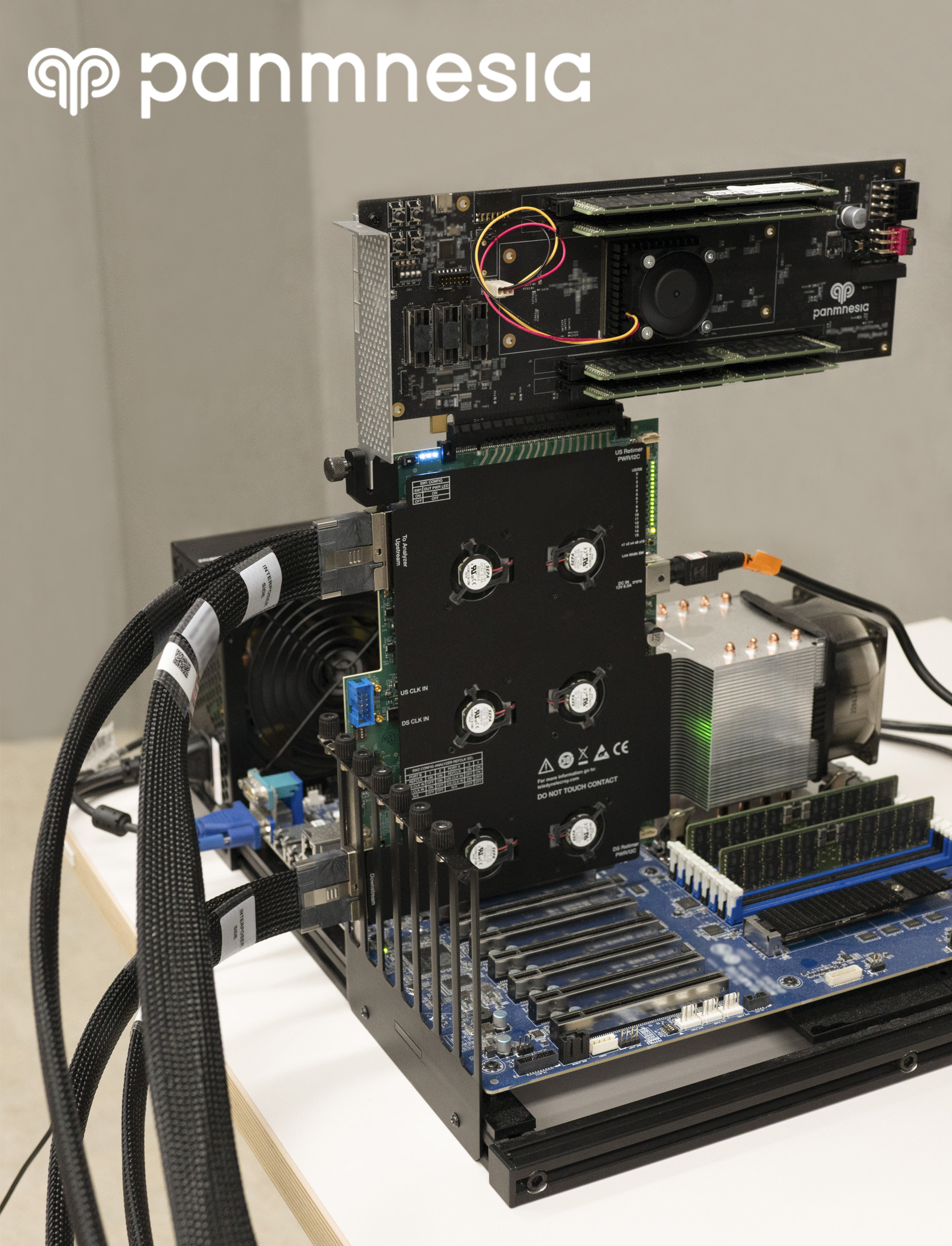

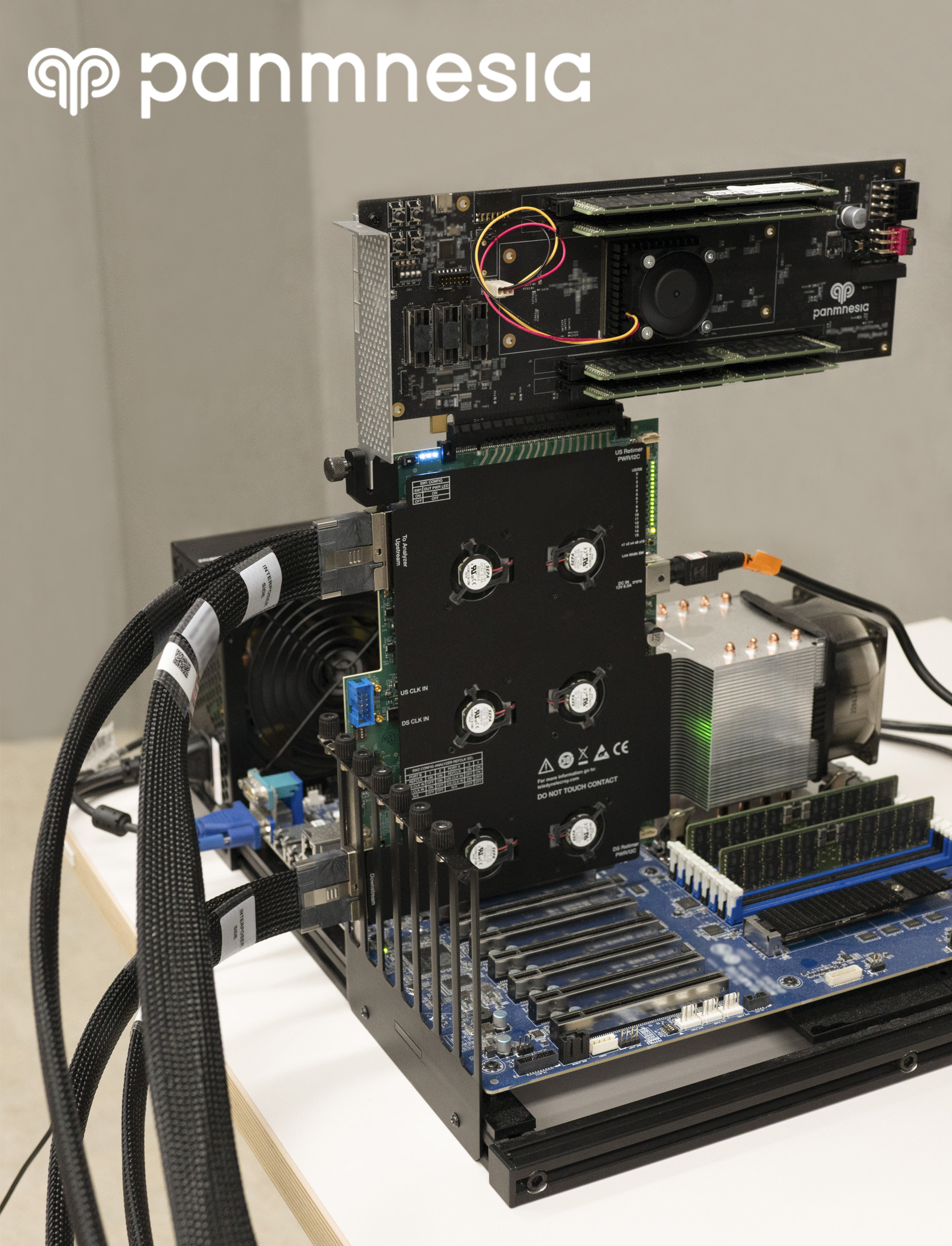

▲파네시아 CXL InterOP 데모 모습 / (사진:파네시아)

DevCon에서 CXL 3.1 스위치 기반 솔루션 발표

“메타·MS·AMD·삼성 등 글로벌 기업에 기술 소개”

최근 글로벌 빅테크 기업들의 초거대 AI 개발 전쟁이 본격화하고 있다. 이에 더해 초거대 AI가 더 크고 복잡한 모델로 진화할수록 AI 가속기와 메모리 확장 요구는 필연적일 수밖에 없다. 이를 해결하는 CXL(Compute Express Link)는 차세대 인터페이스 기술로 글로벌 대기업들이 앞다퉈 CXL 기술 개발과 생태계 구축에 나서고 있는 상황이다.

23일 국내 팹리스 기업 파네시아가 한국 스타트업 가운데 최초로 CXL 상호운용성을 세계 무대에서 검증 시연할 예정이라고 밝혔다. 제1회 CXL 컨소시엄 개발자 컨퍼런스 2024(CXL DevCon 2024)애 참여해 차세대 CXL 3.1 스위치 기반 솔루션을 발표한다.

■ 차세대 반도체 기술 ‘CXL’

CXL는 메모리 관리에 필요한 캐시 일관성 관리와 같은 일련의 동작을 자동으로 보장해준다. 장치의 필요에 맞춰 유연하게 메모리를 확장할 수 있어 데이터센터의 성능과 효율성을 최적화할 수 있는 기술인 것이다.

성능 효율을 높이고 가격 또한 저렴해 최근 마이크로소프트(MS), 메타 등 글로벌 빅테크 기업들의 관심을 한몸에 받고 있다.

CXL은 표준 제정을 통해 실용성을 강화하고 있는데 2019년 CXL 1.0이 제안된 이후 CXL 스위치를 활용한 개선된 확장성의 CXL 2.0 표준이 제정됐다. 최근엔 메모리를 여러 사용자 사이에서 공유하는 기능을 지원해 메모리 자원 활용도를 극대화하는 CXL 3.0과 3.1 표준이 발표됐다.

현재 인텔, AMD 등 글로벌 대기업들이 CXL 기술 개발에 집중하고 있으며, CXL 생태계 구축을 목표로 시스템 장치 제조사 간에 CXL 표준에 맞추어 올바르게 동작되는지 여부를 확인하는 상호운용성 검증 등의 노력이 요구되고 있다.

■ CXL 상호 운용성 검증과 CXL 3.1 IP 올인원 프레임워크

▲

파네시아 CXL InterOP 데모 모습 / (사진:파네시아)

파네시아는 CXL 반도체 팹리스 스타트업으로 CXL IP와 스위치를 개발해 공급한다. IP는 다양한 시스템 장치에 CXL 기술을 도입할 수 있도록 CXL 인터페이스 기능을 회로블록으로 구현했다.

AI 반도체, 메모리 반도체 등 칩을 개발함과 동시에 파네시아는 CXL 3.1 IP를 라이선싱해 제품 개발에 활용할 수 있도록 지원한다. 현재 Arm, HPE 등 글로벌 기업들과의 CXL 관련 협업을 논의하고 있다고 밝혔다.

현재는 CXL 3.1 IP 기반 시제품 제작(Tape Out)이 완료된 것으로 전해진다. 파네시아는 현지시각 기준 4월 30일부터 이틀간 미국 캘리포니아주 산타클라라 매리언트 5번 부스에서 전시를 운영할 예정으로 CXL IP 상호운용성 검증 데모를 이곳에서 선보일 예정이다.

상호운용성 검증 데모는 파네시아 CXL IP를 활용해 개발한 CXL 장치가 컨소시엄에서 발표한 CXL 표준에 맞춰 잘 동작하는지, 인텔/AMD CXL CPU와 안정적으로 호환되는지 검증하는 절차로 구성된다. 이는 국내 스타트업으로서는 최초의 도전이다.

더불어 CXL 3.1 올인원 프레임워크도 함께 전시될 예정이다. CXL 3.1 올인원 프레임워크는 CXL 3.1 IP 기반의 CXL CPU, 스위치, 메모리 확장 장치 및 소프트웨어를 제공한다.

파네시아 관계자는 CXL 3.1 올인원 프레임워크가 멀티-레벨 스위치, 메모리 공유와 같은 CXL 3.1의 주요 기능을 지원해 수 테라바이트 용량의 메모리를 제공하고 메모리 활용도를 최대화할 수 있다고 설명했다.

■ 파네시아 CXL 상호운용성 검증 데모 DevCon서 공개

파네시아는 올해 최초로 개최되는 CXL DevCon 2024에서 CXL 3.1 스위치 기반 솔루션을 발표한다. 권미령 CSO가 연사로 나와 CXL 3.1 스위치 기술을 소개하고 관련 데모를 선보일 예정이다.

CXL 3.1 시스템 내 장치들을 사용자가 원하는 대로 연결해주는 하드웨어 장치로 자유로운 연결관계를 구성했다. CXL 3.1 스위치는 패브릭 매니저 스프트웨어가 내부 라우팅 규칙을 관리할 수 있게 설계됐다. 이를 통해 사용자는 CXL 시스템을 대규모로 확장하기 용이하다.

권미령 CSO는 “우리가 발표하는 기술은 생성형 AI와 같은 빅데이터 서비스 가속 효율성을 최적화하기에 필수적이다”라며 “DevCon 이후 메타에서 열리는 미팅에서 메타, MS, 인텔, AMD, 마이크론, HPE, 마벨, 삼성, 하이닉스 등 글로벌 기업 임원들에게 파네시아의 혁신 기술과 비전을 선보일 것”이라고 말했다.

한편, 파네시아는 CXL 컨소시엄 멤버로 활동하고 있으며, 인텔, 엔비디아, AMD, 마이크로소프트, 메타, IBM 등도 CXL 컨소시엄 멤버로 참여하고 있다.

.jpg)