2.1GHz에서 –81.36dBc 기록… 링 VCO 기반 ILCM 성능 개선, IEEE JSSC 게재

반도체 칩의 고속 작동을 좌우하는 클록 신호에서 참조 스퍼를 최소화한 초소형·저전력 회로 기술이 개발됐다. 5G·6G 통신칩과 AI 칩처럼 대량 데이터를 고속 처리하는 환경에서 요구되는 고품질 클록 신호 구현 성능을 수치로 입증했다.

UNIST 전기전자공학과 윤희인 교수 연구팀은 11일 잡음을 크게 줄인 ILCM(Injection-Locked Clock Multiplier) 기반 클록 신호 생성 반도체 회로를 개발했다고 밝혔다. 연구 결과는 IEEE 반도체 회로 분야 학술지 ‘저널 오브 솔리드 스테이트 서킷(Journal of Solid-State Circuits)’ 2월 6일자에 게재됐다.

■ 참조 스퍼 억제 설계 적용

반도체 칩은 주기적 전기 신호인 클록에 맞춰 동작한다. 고속 통신과 AI 연산 환경에서는 클록 신호의 지터와 참조 스퍼 등 잡음 특성이 시스템 성능에 직접적인 영향을 준다. ILCM 방식은 지터를 줄이는 데 유리하지만, 참조 신호 주입 과정에서 참조 스퍼가 발생하는 한계가 있다.

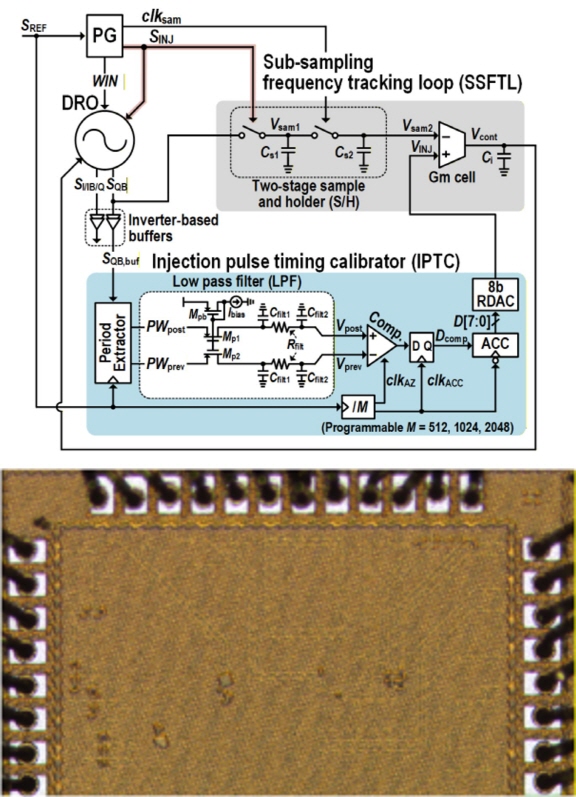

연구팀은 링 발진기(Ring VCO) 기반 ILCM 구조를 채택하고, 주파수 추적(SSFTL)과 기준 신호 주입 타이밍 보정(IPTC) 설계를 적용해 참조 스퍼를 최소화했다.

■ 2.1GHz서 –81.36dBc·지터 280.9fs

개발된 회로는 2.1GHz 출력 조건에서 –81.36dBc의 참조 스퍼를 기록했다. 이는 보고된 링 발진기 기반 ILCM 회로 중 최저 수준이다. 지터는 280.9펨토초(fs)를 달성했다.

28nm CMOS 공정 기준 회로 면적은 0.0444mm², 전력 소모는 12.28mW로 집적도와 전력 효율을 동시에 확보했다. 연구팀은 해당 기술이 6G 통신, AI 칩, 고속 인터커넥트용 클록 소스에 활용될 수 있다고 설명했다.

이번 연구에는 남현준, 안효경 연구원이 제1저자로 참여했다. 연구는 과학기술정보통신부, 반도체설계교육센터(IDEC), 정보통신기획평가원(IITP)의 ‘지역지능화혁신인재양성사업’ 지원을 받아 수행됐다.