EEWEBINAR

최신기사

-

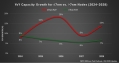

AI 수요 폭증 반도체 생산능력 69% 증가

AI 수요 폭증 반도체 생산능력 69% 증가

-

.jpg) “LiDAR, 자유롭고 안전한 주행 위한 필수 ‘안전장치’”

“LiDAR, 자유롭고 안전한 주행 위한 필수 ‘안전장치’”

-

.jpg) 노르딕, 정밀 연료 게이지 탑재로 에너지 효율·사용자 경험 극대화

노르딕, 정밀 연료 게이지 탑재로 에너지 효율·사용자 경험 극대화

-

.jpg) [전자기기 열관리 혁신] ① 칩 저항기, 발열을 간과하면 생기는 일

[전자기기 열관리 혁신] ① 칩 저항기, 발열을 간과하면 생기는 일

-

ETRI, 차세대 UAM 위한 핵심 인프라 확보

-

티이엠씨, 저탄소 HFO 국산화 반도체 식각 친환경 혁신 본격화

티이엠씨, 저탄소 HFO 국산화 반도체 식각 친환경 혁신 본격화

-

“자율주행·SDV, 제품 차별화 중심 급부상”

“자율주행·SDV, 제품 차별화 중심 급부상”

-

슈나이더, 엔비디아와 차세대 AI 팩토리 구축 박차

슈나이더, 엔비디아와 차세대 AI 팩토리 구축 박차

-

ST, 복잡한 차량 부하 해결 기대

ST, 복잡한 차량 부하 해결 기대

-

.jpg) 기계식 퓨즈를 넘어, 전자식 보호 소자의 시대 - 인피니언의 Wire Guar..

기계식 퓨즈를 넘어, 전자식 보호 소자의 시대 - 인피니언의 Wire Guar..

Sponsored Links

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 강정규 070-4699-5321 , news@e4ds.com