어플라이드 머티어리얼즈가 그동안 연구 단계에서 많이 거론돼 온 루테늄(Ru)을 양산 과정에서 활용해 전력소모를 25% 낮추고, 공극 저항을 줄여 2나노 이하의 첨단 반도체 공정에 적용할 수 있는 기술을 반도체 메이커에 이미 공급하고 있다고 밝혀 향후 초미세 반도체 제조 공정에서 혁신이 가속화 될 것으로 기대를 모으고 있다.

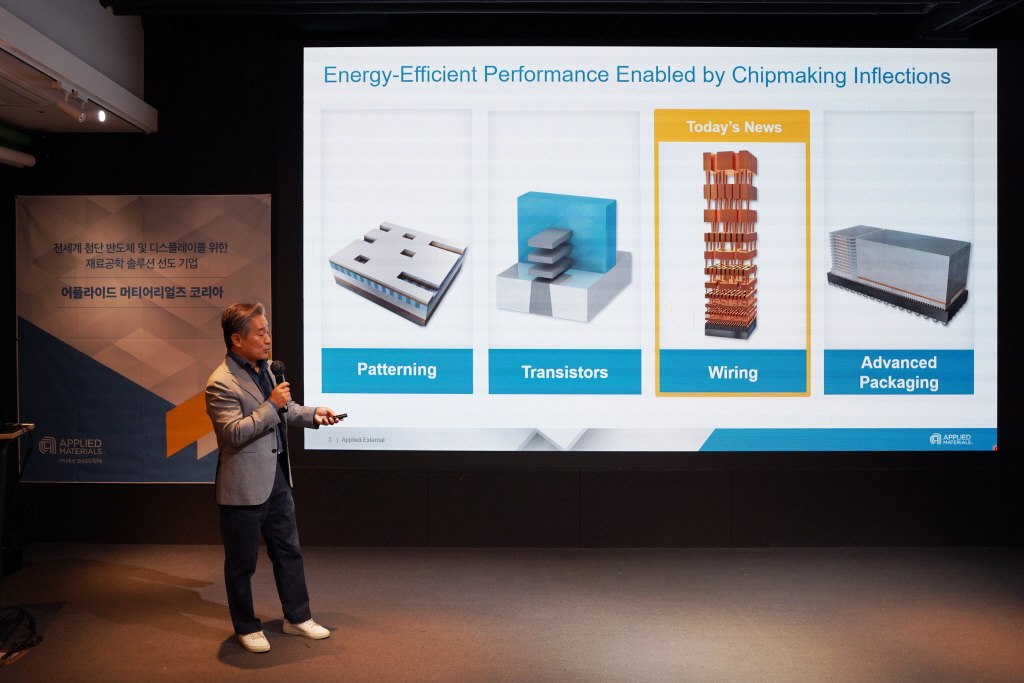

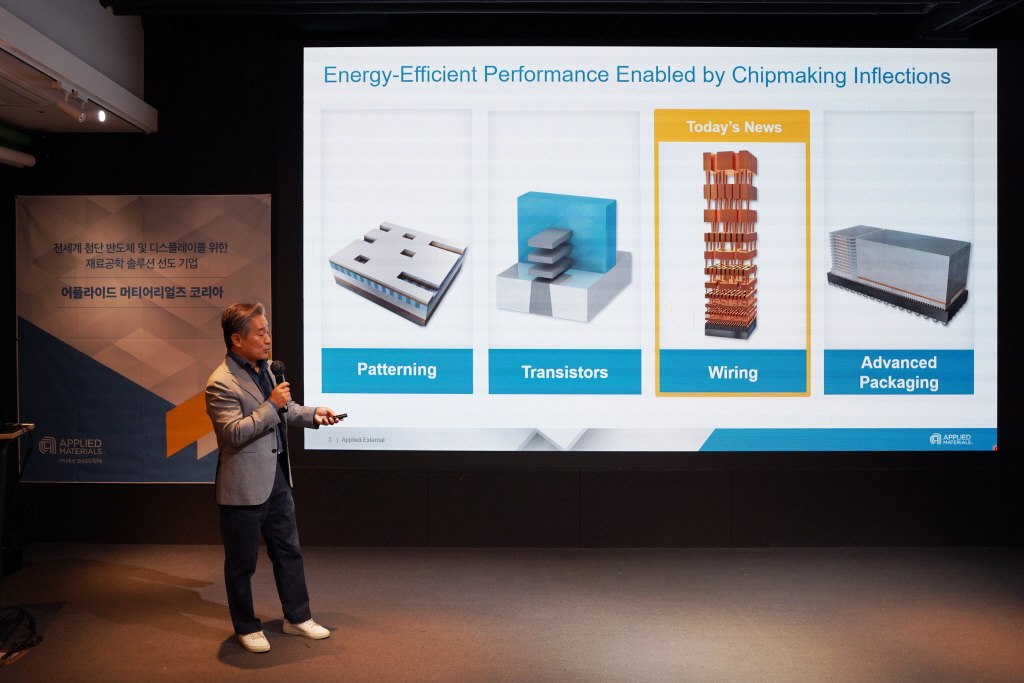

▲이은기 어플라이드 머티어리얼즈 박막 기술 총괄이 발표를 하고 있다.

엔듀라 쿠퍼 배리어 씨드 IMS, 챔버들 하나로 연결 공정기술 개선

블랙 다이아몬드, 유전율 감소·물리적 물성 높여 패키징 손상 줄여

어플라이드 머티어리얼즈가 그동안 연구 단계에서 많이 거론돼 온 루테늄(Ru)을 양산 과정에서 활용해 전력소모를 25% 낮추고, 공극 저항을 줄여 2나노 이하의 첨단 반도체 공정에 적용할 수 있는 기술을 반도체 메이커에 이미 공급하고 있다고 밝혀 향후 초미세 반도체 제조 공정에서 혁신이 가속화 될 것으로 기대를 모으고 있다.

어플라이드는 14일 기자간담회를 통해 2나노(㎚) 로직 노드 이하로 구리 배선 스케일링을 가능케 함으로써 컴퓨터 시스템 와트당 성능을 높이는 재료공학 혁신을 발표했다.

이날 간담회에서는 이은기 박막 기술 총괄이 발표를 담당했다.

이은기 총괄에 따르면 배선라인은 디바이스가 작아지면 저항이 늘어나서 스피드가 떨어지고, 정전용량이 늘어나서 파워소모가 큰데 AI 시대에는 에너지 효율이 더욱 높은 컴퓨팅이 요구되고, 성능 및 전력 소비에서 칩 배선과 적층이 매우 중요하다고 밝혔다.

이를 개선하기 위해 어플라이드는 기존의 코발트 유전체를 코발트(Co)와 루테늄(Ru)을 이용한 소재로 개선해 기존의 30옹스토롱에 달하던 배선을 20옹스트롱으로 줄여 공간을 반으로 줄이고, 구리용량을 30% 증가 시켜 전력효율을 좋게 개선했다고 밝혔다.

특히 코발트 두께를 줄이면, 보이드(공극)이 생길 수 있는데, 보이드가 안 생기도록 진공상태에서 챔버들을 하나로 연결된 엔듀라 쿠퍼 배리어 씨드 IMS 시스템을 구현해 단순히 루테늄을 쓰는 게 아니라 공정기술을 통해 전기 배선 저항을 최대 25%까지 낮춰 칩 성능과 전력 소비를 개선했다고 언급했다.

또한 엔듀라 쿠퍼 배리어 씨드 IMS는 모든 선도 로직 반도체 제조사가 채택해 3나노로 고객 출하를 시작한 것으로 밝혔다.

이와 함께 로우 K 유전체 기술도 향상됐는데 배선과 배선 사이의 절연체는 유전상수(K)를 줄일수록 물리적 물성이 나빠지는데 이를 극복하기 위해 어플라이드는 ‘블랙 다이아몬드’ 소재 기술로 유전율도 낮추고, 물리적 물성도 높여 패키징시 손상을 줄였다.

이를 통해 전력 효율을 극대화하고, 2나노 이하의 스케일링을 가능하게 해 반도체 제조사 및 시스템 업체가 3D 로직과 메모리 적층의 차원을 높이는데 있어 매우 중요해진 기계적 강성을 구현해 많은 로직 및 D램 기업들이 채택하고 있는 것으로 알려졌다.

이은기 박막 총괄은 “이번 재료공학 혁신을 통해 반도체 메이커들이 기본적으로 수율을 높이고, 신뢰성을 높이는데 기여했다”며 “2나노 이하 첨단 인터커넥트 배선 공정에서 기술 최첨단 기술을 제공 할 수 있도록 노력하겠다”고 밝혔다.