인텔, nm 대신할 공정 이름에 7/4/3/20A 채택

'24년 20A(2nm) 제품에 리본펫, 파워비아 도입

ASML과 협력 발표, 퀄컴-AWS, IFS 첫 고객돼

예상치를 뛰어넘는 2분기 매출을 기록한 인텔이 현지 시각으로 26일, 10nm 이하 공정 도입 시기와 파운드리 사업에 대한 계획을 밝혔다.

팻 겔싱어(Pat Gelsinger) 인텔 CEO는 ‘인텔 엑셀러레이티드(Intel Accelerated)’ 행사에서 “업계에선 1997년부터 나노미터(nm) 기반 공정의 (7nm, 5nm 같은) 명칭이 실제 게이트 길이와 일치하지 않는다는 사실을 알고 있다”라며 고객이 나노 공정을 정확하게 파악할 수 있도록 ‘인텔 7/4/3/20A’ 명칭을 도입했다 밝혔다.

▲ 인텔 엑셀러레이티드 행사를 진행 중인

팻 겔싱어 인텔 CEO [사진=인텔]

인텔에 따르면, 인텔 7 공정은 TSMC나 삼성전자의 7nm 공정, 인텔 4/3 공정은 4/3nm 공정, 인텔 20A 공정은 2nm 공정에 대응한다. 인텔 7 기반 제품은 클라이언트용으론 올해 출시될 ‘앨더 레이크(Alder Lake)’ 프로세서에, 데이터센터용으론 내년 1분기 생산 예정인 ‘사파이어 래피즈(Sapphire Rapids)’에 적용된다. 인텔 4 공정부턴 EUV 장비가 도입되며, 2023년 상반기 제품 출하가 목표다.

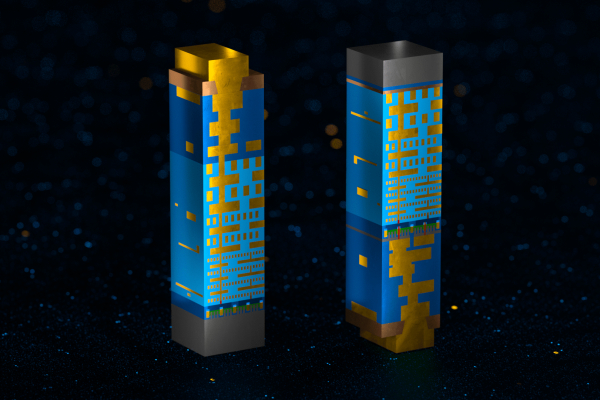

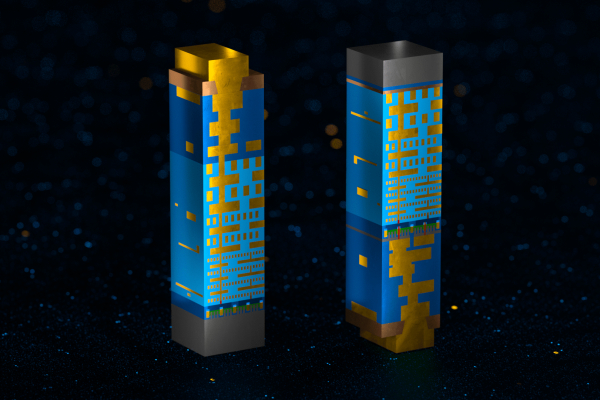

4 대비 핀펫(FinFET) 최적화가 들어간 3 공정은 2023년 하반기 제품 출하가 목표다. 20A 공정은 1nm 이하인 옹스트롬(Ångström; 0.1nm) 단위의 공정에 돌입하기 위한 준비로, ‘리본펫(RibbonFET)’과 ‘파워비아(PowerVia)’ 기술이 도입된다. 리본펫은 인텔만의 GAA(Gate-all-around) 트랜지스터 아키텍처 명칭이며, 파워비아는 신호 전송과 전력 공급을 웨이퍼 전면과 후면에 할당하는 기술이다.

▲ 파워비아 기술은 신호 전송 구역을 웨이퍼 전면에 배치하고,

전력 공급 구역을 웨이퍼 후면에 배치해서 양산하는 것으로,

아직 양산 단계에서 적용된 사례는 없다 [그림=인텔]

20A 제품은 2024년 생산이 목표로, 첫 고객은 퀄컴일 예정이다. 인텔은 2025년 초 ‘인텔 18A’ 기반 제품을 생산할 계획으로, 이를 위한 ‘고해상력(High-NA) EUV’ 기술을 개발하기 위해 ASML과 긴밀하게 협업하고 있다고 밝혔다.

갤싱어 CEO는 “아마존웹서비스(AWS)가 인텔 파운드리 서비스(Intel Foundry Service; IFS) 패키징 솔루션의 첫 고객이 될 것”이라며, 3D 적층 솔루션인 ‘포베로스(Foveros)’를 강조했다. 또한, 이를 개선한 ‘포베로스 옴니(Omni) 및 포베로스 다이렉트(Direct)’ 솔루션이 2023년에 각각 생산 및 준비될 예정이라 밝혔다.